# DS1206 Phantom Serial Interface Chip

#### **FEATURES**

- Minimum expense add-on serial port

- Converts standard bytewide or DRAM memory waveforms into a 3-wire serial port

- Operation is transparent to memory

- Software–generated memory cycles activate serial port and transfer data

- High bandwidth 1-bit data transfer per two memory cycles

- Intercepts memory signals so that pass-through connections to memory can be maintained

- Controls communications for as many as ten DS1201 Electronic Tags, DS1204U Electronic Keys, DS1207 TimeKeys or DS1290 Eliminators

- Low-power CMOS circuitry

- Optional 16-pin SOIC surface mount package

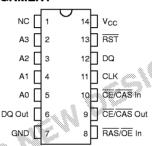

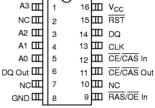

#### **PIN ASSIGNMENT**

4-PIN DIP (300 MIL) See Mech. Drawings Section

16-PIN SOIC (300 MIL) See Mech. Drawings Section

### **PIN DESCRIPTION**

NC – No Connection

A0–A3 – Memory Address Bus

DQ Out – Data Out To Memory Bus

GND - Ground

RAS/OE In - Output Enable or RAS input from

memory bus

CE/CAS In - Chip enable or CAS from memory bus CE/CAS Out - Chip enable or CAS to memory circuit

CLK - Clock for Serial Port

DQ - Data I/O for Serial Port

RST - Reset for Serial Port

V<sub>CC</sub> - +5 Volts

#### **DESCRIPTION**

The DS1206 Phantom Serial Interface Chip is a CMOS circuit which intercepts the standardized memory bus found in computer systems and adapts the bus to a 3-wire serial port. Multiple memory cycles are used as a basis for generating the appropriate signals to control the serial port. A sequence of software-generated

memory cycles encodes commands and transfers data with low pin count. The serial port signaling is derived from the memory address bus lines A0 through A3, the CE/CAS signal and RAS/OE signal without affecting address space, thereby maintaining transparency to the memory bus. Communications are established under

software control by an address pattern recognition sequence (serial port protocol) which disables a bytewide or DRAM memory via  $\overline{CE/CAS}$  output. An additional address sequence is required to generate the 3–wire port signals:  $\overline{RESET}$  ( $\overline{RST}$ ), Data (DQ), and Clock (CLK). The add–on serial port provides a minimum cost interface to the DS1201, DS1204U, DS1207, DS1223, and DS1290.

#### **OPERATION**

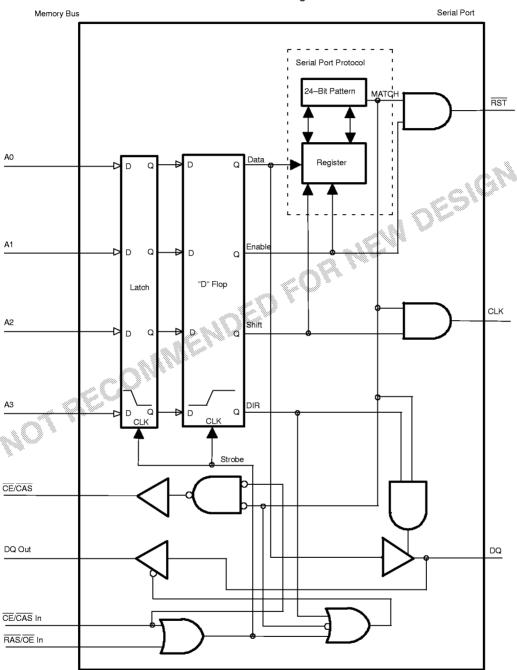

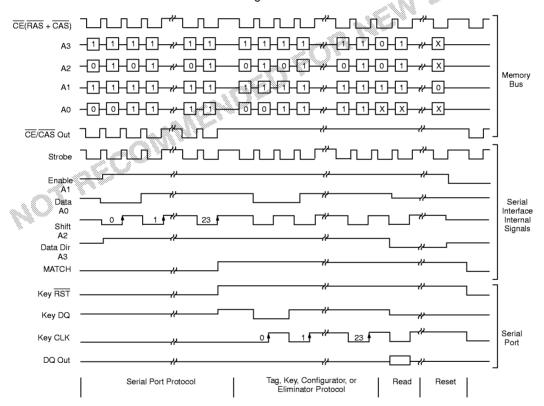

The main parts of the DS1206 are shown in the block diagram of Figure 1. Information presented on address inputs is latched into the DS1206 on the falling edge of a strobe signal derived from the logical combination of CE/CAS In and RAS/OE In. When redirecting information from a DRAM memory bus, both RAS and CAS inputs are required and the column addresses are used for signaling.

For a bytewide memory bus, only a  $\overline{\text{CE}}$  input is required and the  $\overline{\text{RAS/OE}}$  input can be tied low or connected to the memory  $\overline{\text{OE}}$  input signal. The rising edge of the strobe will cause the address information to be presented for comparison to the 4-bit serial interface protocol and to logic which will generate signals for the serial port. The serial interface protocol is derived from address inputs A0, A1, and A2.

A1 is an enable signal which activates the communications sequence. A0 defines the data which is compared for recognition. A2 is used to clock in information defined by A0. Initially the A1 input must be set high to enable serial interface communications. A1 must remain high during the pattern recognition sequence and subsequent communications with the serial port after the protocol pattern match is established. If the A1 input is set low, all communications are terminated and future access to the serial port is denied.

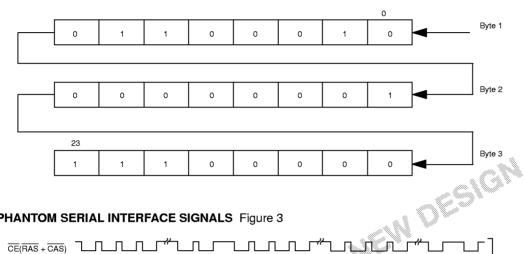

Data transfer through the serial interface occurs by matching a 24-bit pattern as shown in Figure 2. This pattern is presented to a register on each rising edge of strobe. Data is input for comparison to the serial interface protocol at the end of each memory cycle (see Figure 3). The proper information must be presented on A0 to match the 24-bit pattern while keeping A1 high. Address input A2 is used to generate the shift signal which causes data to enter the 24-bit register for comparison to the 24-bit pattern. Information is loaded one bit at a time on the rising edge of shift. Each shift cycle must be generated from two memory cycles.

The first memory cycle sets A2 low and establishes the shift clock low. The second memory cycle sets A2 high and causes the transition necessary to shift a bit of data into the 24-bit register. Data on A0 is kept at the correct level for both memory cycles. Address input A3 is used to control the direction of data going to and from the serial port. This input is not used during pattern recognition of the protocol. After the 24-bit pattern has been correctly entered, a match signal is generated. The match signal is logically combined with the enable signal to generate the RST signal for the serial port. The match signal is also used to disable Chip Enable to the memory bus and to enable a gate which allows the serial port DQ to drive the DQ out line to the memory bus.

When RST is driven high, devices attached to the serial port become active. Subsequent shift signals derived from A2 will now be recognized as the serial port clock. The data signal for the serial bus is derived from A0 conditioned on the level of the direction signal derived from A3. When A3 is set high, data as defined by A0 will be sent out on the serial port DQ. When A3 is set low, devices attached to the serial port can drive the memory bus DQ out line. The data direction bit must be set low when reading data from the serial port DQ.

# PHANTOM SERIAL INTERFACE BLOCK DIAGRAM Figure 1

### SERIAL INTERFACE 24-BIT PROTOCOL Figure 2

# PHANTOM SERIAL INTERFACE SIGNALS Figure 3

### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on any Pin Relative to Ground —0.5V to +7.0V

Operating Temperature 0°C to 70°C

Storage Temperature —55°C to +125°C

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

### RECOMMENDED DC OPERATING CONDITIONS

(0°C to 70°C)

| PARAMETER | SYMBOL          | MIN  | TYP | MAX                   | UNITS | NOTES |

|-----------|-----------------|------|-----|-----------------------|-------|-------|

| Logic 1   | V <sub>IH</sub> | 2.0  |     | V <sub>CC</sub> + 0.3 | V     | 1     |

| Logic 0   | V <sub>IL</sub> | -0.3 |     | +0.8                  | V     | 1     |

| Supply    | V <sub>CC</sub> | 4.5  | 5.0 | 5.5                   | ٧     |       |

### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}\text{C to }70^{\circ}\text{C}; V_{DD} = 5\text{V} \pm 10\%)$

| PARAMETER                 | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|---------------------------|------------------|-----|-----|-----|-------|-------|

| Input Leakage             | I <sub>IL</sub>  | -1  |     | +1  | μА    |       |

| Output Leakage            | ILO              |     |     | 1   | μΑ    |       |

| Output Current @ 2.4V     | l <sub>OH</sub>  | -1  |     |     | mA    |       |

| Output Current @ 0.4V     | lor<br>lor       | +4  |     |     | mA    |       |

| RST Output Current @ 3.8V | l <sub>OHR</sub> | 16  |     |     | mA    |       |

| Supply Current            | Icc              |     |     | 6   | mA    | 2     |

CAPACITANCE (t<sub>A</sub>=25°C)

| PARAMETER         | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|-------------------|------------------|-----|-----|-----|-------|-------|

| Input Capacitance | C <sub>IN</sub>  |     | 5   | 10  | pF    |       |

| Input/Output      | C <sub>I/O</sub> |     | 5   | 10  | pF    |       |

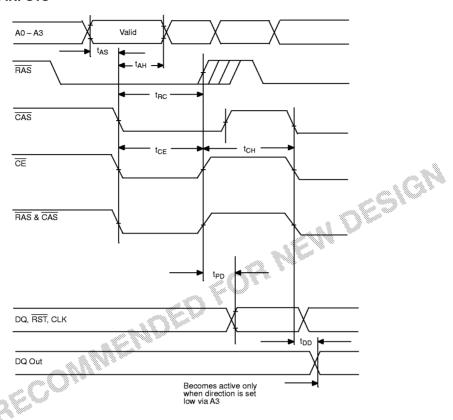

### AC ELECTRICAL CHARACTERISTICS

$(0^{\circ}\text{C to }70^{\circ}\text{C}; V_{\text{CC}} = 5\text{V} \pm 10\%)$

| PARAMETER          | SYMBOL          | MIN | TYP | MAX | UNITS | NOTES |

|--------------------|-----------------|-----|-----|-----|-------|-------|

| Address Setup      | t <sub>AS</sub> | 0   |     |     | ns    |       |

| Address Hold       | t <sub>AH</sub> | 50  |     |     | ns    |       |

| RAS to CAS Overlap | t <sub>RC</sub> | 60  |     |     | ns    |       |

| CE Pulse Width     | t <sub>CE</sub> | 60  |     |     | ns    |       |

| Key Signals Valid  | t <sub>PD</sub> |     |     | 60  | ns    | 3     |

| Key Data Out       | t <sub>DD</sub> | 10  |     |     | ns    | 3     |

| CE Inactive        | t <sub>CH</sub> | 30  |     |     | ns    |       |

### **MEMORY BUS INPUTS**

### NOTES:

- 1. All voltages are referenced to ground.

- 2. Measured with outputs open.

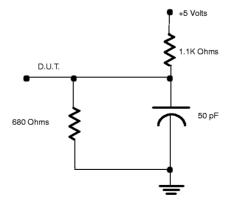

- 3. Measured with a load as shown in Figure 4.

# **OUTPUT LOAD** Figure 4

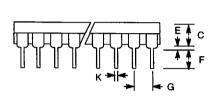

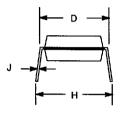

### 8- TO 28-PIN DIP (300 MIL)

| DS1211   | DS1621                                                                                                                                 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| DS1215   | DS1625                                                                                                                                 |

| DS1221   | DS1632                                                                                                                                 |

| DS1222   | DS1640                                                                                                                                 |

| DS1228   | DS1651                                                                                                                                 |

| DS1229   | DS1652                                                                                                                                 |

| DS1231   | DS1652B                                                                                                                                |

| DS1232   | DS1653                                                                                                                                 |

| DS1232LP | DS1666                                                                                                                                 |

| DS1234   | DS1667                                                                                                                                 |

| DS1236   | DS1669                                                                                                                                 |

| DS1237   | DS1802                                                                                                                                 |

| DS1238   | DS1830                                                                                                                                 |

| DS1239   | DS1832                                                                                                                                 |

| DS1259   | DS1867                                                                                                                                 |

| DS1267   | DS1868                                                                                                                                 |

| DS1275   | DS1869                                                                                                                                 |

| DS1291   | DS2009D                                                                                                                                |

| DS1293   | DS2010D                                                                                                                                |

| DS1336   | DS2011D                                                                                                                                |

| DS1620   | DS2013D                                                                                                                                |

|          | DS1215 DS1221 DS1222 DS1228 DS1229 DS1231 DS1232 DS1232LP DS1236 DS1237 DS1238 DS1239 DS1239 DS1259 DS1267 DS1275 DS1291 DS1293 DS1293 |

| PKG   | 8-PIN |       | 10-PIN |       | 14-PIN |       | 16-PIN |       |

|-------|-------|-------|--------|-------|--------|-------|--------|-------|

| DIM   | MIN   | MAX   | MIN    | MAX   | MIN    | MAX   | MIN    | MAX   |

| A IN. | 0.360 | 0.400 | 0.480  | 0.520 | 0.740  | 0.780 | 0.740  | 0.780 |

| MM    | 9.14  | 10.16 | 12.19  | 13.21 | 18.80  | 19.81 | 18.80  | 19.81 |

| B IN. | 0.240 | 0.260 | 0.240  | 0.260 | 0.240  | 0.260 | 0.240  | 0.260 |

| MM    | 6.10  | 6.60  | 6.10   | 6.60  | 6.10   | 6.60  | 6.10   | 6.60  |

| C IN. | 0.120 | 0.140 | 0.120  | 0.140 | 0.120  | 0.140 | 0.120  | 0.140 |

| MM    | 3.05  | 3.56  | 3.05   | 3.56  | 3.05   | 3.56  | 3.05   | 3.56  |

| D IN. | 0.300 | 0.325 | 0.300  | 0.325 | 0.300  | 0.325 | 0.300  | 0.325 |

| MM    | 7.62  | 8.26  | 7.62   | 8.26  | 7.62   | 8.26  | 7.62   | 8.26  |

| E IN. | 0.015 | 0.040 | 0.015  | 0.040 | 0.015  | 0.040 | 0.015  | 0.040 |

| MM    | 0.38  | 1.02  | 0.38   | 1.02  | 0.38   | 1.02  | 0.38   | 1.02  |

| F IN. | 0.120 | 0.140 | 0.110  | 0.130 | 0.120  | 0.140 | 0.120  | 0.140 |

| MM    | 3.04  | 3.56  | 2.79   | 3.30  | 3.04   | 3.56  | 3.04   | 3.56  |

| G IN. | 0.090 | 0.110 | 0.090  | 0.110 | 0.090  | 0.110 | 0.090  | 0.110 |

| MM    | 2.29  | 2.79  | 2.29   | 2.79  | 2.29   | 2.79  | 2.29   | 2.79  |

| H IN  | 0.320 | 0.370 | 0.320  | 0.370 | 0.320  | 0.370 | 0.320  | 0.370 |

| MM    | 8.13  | 9.40  | 8.13   | 9.40  | 8.13   | 9.40  | 8.13   | 9.40  |

| J IN  | 0.008 | 0.012 | 0.008  | 0.012 | 0.008  | 0.012 | 0.008  | 0.012 |

| MM    | 0.20  | 0.30  | 0.20   | 0.30  | 0.20   | 0.30  | 0.20   | 0.30  |

| K IN. | 0.015 | 0.021 | 0.015  | 0.021 | 0.015  | 0.021 | 0.015  | 0.021 |

| MM    | 0.38  | 0.53  | 0.38   | 0.53  | 0.38   | 0.53  | 0.38   | 0.53  |

Continued on following page.

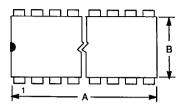

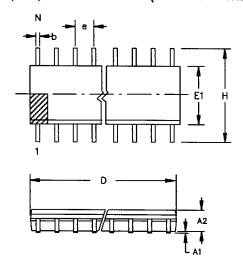

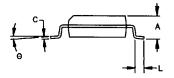

# MECHANICAL DRAWINGS

# 8-, 14-, AND 16-PIN SOIC (.150" BODY WIDTH)

| PKG    | 8-F   | PIN   | 14-       | PIN   | 16-       | PIN   |

|--------|-------|-------|-----------|-------|-----------|-------|

| DIM    | MIN   | MAX   | MIN       | MAX   | MIN       | MAX   |

| A IN.  | 0.053 | 0.069 | 0.053     | 0.069 | 0.053     | 0.069 |

| MM     | 1.35  | 1.75  | 1.35      | 1.75  | 1.35      | 1.75  |

| A1 IN. | 0.004 | 0.010 | 0.004     | 0.010 | 0.004     | 0.010 |

| MM     | 0.10  | 0.25  | 0.10      | 0.25  | 0.10      | 0.25  |

| A2 IN. | 0.048 | 0.062 | 0.048     | 0.062 | 0.048     | 0.062 |

| MM     | 1.24  | 1.57  | 1.24      | 1.57  | 1.24      | 1.57  |

| b IN.  | 0.012 | 0.020 | 0.012     | 0.020 | 0.012     | 0.020 |

| MM     | 0.030 | 0.50  | 0.30      | 0.50  | 0.30      | 0.50  |

| C IN   | 0.007 | 0.011 | 0.007     | 0.011 | 0.007     | 0.011 |

| MM     | 0.17  | 0.28  | 0.17      | 0.28  | 0.17      | 0.28  |

| D IN.  | 0.188 | 0.196 | 0.337     | 0.344 | 0.386     | 0.393 |

| MM     | 4.78  | 4.98  | 8.55      | 8.74  | 9.80      | 9.98  |

| e IN.  |       | BSC   | 0.050 BSC |       | 0.050 BSC |       |

| MM     |       | BSC   | 1.27 BSC  |       | 1.27 BSC  |       |

| E1 IN. | 0.150 | 0.158 | 0.150     | 0.158 | 0.150     | 0.158 |

| MM     | 3.81  | 4.01  | 3.81      | 4.01  | 3.81      | 4.01  |

| H IN.  | 0.230 | 0.244 | 0.230     | 0.244 | 0.230     | 0.244 |

| MM     | 5.84  | 6.20  | 5.84      | 6.20  | 5.84      | 6.20  |

| L IN.  | 0.016 | 0.050 | 0.016     | 0.050 | 0.016     | 0.050 |

| MM     | 0.40  | 0.89  | 0.40      | 0.89  | 0.40      | 0.89  |

| Θ      | 0°    | 8°    | 0°        | 8°    | 0°        | 8°    |