o Serial data output for easy inter-

face with microcomputer

#### UNIVERSAL PCM-IR-REMOTE CONTROL RECEIVER

Technology: N-MOS, Si-gate

Features:

- o High interference rejection through dual transmission frequencies and several builtin checks within the received words

- o High information transmission rate through low-consumption pulse-code-modulated (PCM) transmission bursts with no word repetition

Case:

8 pin dual inline plastic

#### Absolute maximum ratings

| Referred to V <sub>SS</sub> =ground, OV,            | pin 1   |                    |                          |     |

|-----------------------------------------------------|---------|--------------------|--------------------------|-----|

| Supply voltage                                      | Pin 8   | V <sub>DDmax</sub> | 15                       | ٧   |

| Voltage at the other pins                           | Pin 2-7 | v <sub>N</sub>     | -0.3/+V <sub>DDmax</sub> | ۷   |

| Output current                                      | Pin 6   | <sup>1</sup> 0     | 5                        | mA  |

| Ambient temperature<br>V <sub>S</sub> = 13.2 V      |         | Tamb               | 0 + 85                   | °C  |

| Storage temperature                                 |         | Tstg               | -25 + 125                | °C  |

| Total power dissipation<br>T <sub>amb</sub> = 85 °C |         | Ptot               | 400                      | m₩  |

| Junction temperature                                |         | T <sub>j</sub>     | 125                      | °C  |

| Maximum thermal resistance                          |         |                    |                          |     |

| Junction ambient                                    |         | <sup>R</sup> thJA  | 97                       | K/W |

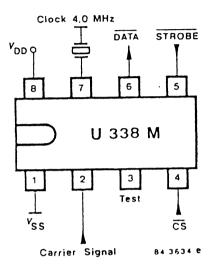

Pin connection

### Description

This N-MOS receiver module demodulates the command words given out by the transmitter U 327 M (IR-transmission) and from them produces the input data (12-bit serial) for a down-stream microcomputer. The serial interface allows the direct connection of the receiver to the I/O ports of microcomputers. An on-chip Ready-FF signal synchronises the orderly data flow between IR-input and DATA-output.

Connections:

Pin 1 V<sub>SS</sub>, ground 0 V

## Pin 2 Carrier-signal input

A command word consists of 13 sequentially arranged segments of the carrier frequency  $F_1 = 34.64$  kHz,  $F_2 = 37.31$  kHz, or of defined pauses. The content of the command word has 13 bits and is pulse-coded, an  $F_1$ -segment representing a logic "L" and an  $F_2$ -segment a logic "H". The length of an  $F_1$ -segment at the beginning of the word and immediately after within-word transmission pauses is 13 pulses, and within the word and directly linked with an  $F_2$ -segment, 12 pulses.

Correspondingly, an  $F_2$ -segment consists of 9 or 8 pulses.

Successive bits of the same value are suppressed at the transmitter and are completed by the receiver. The radiated word ends with the 13th bit, a check-bit, representing the complement of the data bit transmitted immediately before it. Frequency measurement is carrier out by pulse counting within precisely defined time-windows. A count of 10 or 6 periods identifies  $F_1$  or  $F_2$  respectively.

The rejection of interference from the input signal is ensured by the following criteria:

- Frequencies of the word segments

- Length of the word segments

- Sequential order of the word segment

- Position of the segments within the word (Raster)

- Position and contents of the checkbit

- Word length and a minimum following interval free from received signal of 4.3 ms.

Interference during the signal-free minimum interval prevents the the Ready-FF from being set. Thereby the last IR-command is not passed on to the MC.

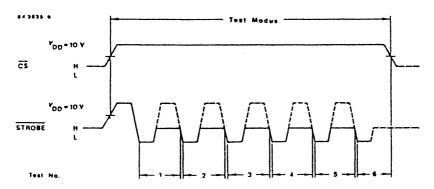

#### Pin 3 Test (Line)

The module is switched to the Test-mode by taking C5 and STROBE to a potential of typically 10 V. The circuit remains in the Test mode as long as C5 is held at 10 V. Depending on an internal counter, which is counted on by pulses at the STROBE input, either various data from the frequency-recognition circuit is given out at Pin 3, or data must be input at Pin 3, to test out the word recognition (see table 1, diagram a).

Table 1:

|          | INPUT                                      |     | ουτρυτ                                                               |     |  |  |  |

|----------|--------------------------------------------|-----|----------------------------------------------------------------------|-----|--|--|--|

| Test-No. | Function                                   | Pin | Function                                                             | Pin |  |  |  |

| 1        | Frequency                                  | 2   | F <sub>1</sub> -single recognition<br>(measurement of double period) | 3   |  |  |  |

| 2        | Frequency                                  | . 2 | F <sub>2</sub> -single recognition<br>(measurement of double period) | 3   |  |  |  |

| 3        | Frequency                                  | 2   | $F_1$ -multiple (bit) recognition<br>(5 x $F_1$ -single recognition) | 3   |  |  |  |

| 4        | Frequency                                  | 2   | $F_2$ -multiple (bit) recognition<br>(3 x $F_2$ -single recognition) | 3   |  |  |  |

| 5        | F <sub>1</sub> -bit                        | 3   | Command word                                                         |     |  |  |  |

| 6        | F <sub>1</sub> -bit<br>F <sub>2</sub> -bit | 3   | Check of error-recognition                                           | 6   |  |  |  |

In the normal operation state, Pin 3 delivers a static line signal (active LOW) in order to switch downstream system components from Stand-by to operating state. Commands and addresses, for which the line-flip-flop is set or reset, can be randomly selected (mask-programmed). 4 terminal lines are available for the selection of addresses or address ranges. The same is true for choice of commands or command-groups.

In the basic version of the U 338 M, lines from the command groups 3 + 4 under address 1 were selected for setting the line flip-flop LOW. Resetting is likewise achieved by command 4 under address 1 (see layout in the tables for address- and command-lines).

57

#### Pin 4

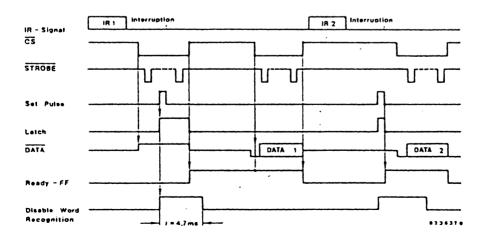

The DATA-output remains high-resistance for as long as US is HIGH. When the microprocessor delivers a chip-select (active LOW), the Ready signal is first switched to the DATA-output line. When Ready is set (LOW), a complete word is ready to be fetched (see diagram c).

The trailing edge of CS resets the Ready-FF (whether the STROBE was presented or not), so that the receiver is ready to accept the next IR-command. If a set-pulse for the Ready-FF arises while CS is active, this set-pulse is temporarily stored and the setting of the ready flip-flop is delayed until CS goes HIGH again (see diagram b).

This ensures that a word coming in during the period of time when the electronics is switched off (CS = LOW) is not last. The delay is in force for a least 4.3 ms, after which the Ready-FF or the buffer store can be reset by a newly-arriving bit, irrespective of whether CS is HIGH or LOW.

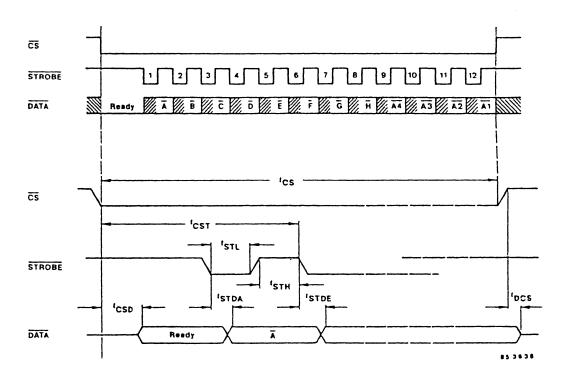

#### Pin 5 STROBE

If C5 is active and Ready is set, a complete data word (12 bit) can be ready by 12 STROBES (see diagram c). If C5 is active but Ready-FF not set, STROBE-pulses do not prevent the formation of a new word (see diagram b).

If no new word is read. STROBE should be kept high.

Diagram b

# Pin 6 DATA

.

The switching on of CS first puts the Ready signal to the data output. With the first STROBE, data bit A appears, and with the twelvth STROBE address-bit A1 (diagram c, table 2). As long as there is an output, no command is accepted.

If there is no CS after receipt of a word, the data word and the Ready signal are retained for a least 4.3 ms, but only however until the receipt of a new word. The Ready-FF can be reset by a newly captured bit, at the earliest, after the elapse of this 4.3 ms period.

Diagram c

.

Table 2:

.

Coding of the data output DATA:

.

a: Command Section

| Dat | ta ou | utput |                                           |                                 |                                                | Command-No.*                                         | Da     | ta o | utput |                                      |                             |                                      | Command-No.*                                 |

|-----|-------|-------|-------------------------------------------|---------------------------------|------------------------------------------------|------------------------------------------------------|--------|------|-------|--------------------------------------|-----------------------------|--------------------------------------|----------------------------------------------|

| F   | ε     | D     | C                                         | B                               | A.                                             | (transmitter)                                        | F      | ε    | D     | С                                    | B                           | A                                    | (transmitter)                                |

| L   | L     | L     | L<br>L<br>L<br>L<br>H<br>H<br>H<br>H<br>H | L<br>H<br>H<br>L<br>H<br>H<br>H | L<br>H<br>L<br>H<br>L<br>H<br>L<br>H           | 0<br>1<br>2<br>3<br>4 **<br>5<br>6<br>7              | Н      | L    | L     | L<br>L<br>L<br>H<br>H<br>H<br>H      | L<br>H H<br>L<br>H H<br>H H | L<br>H<br>L<br>H<br>L<br>H<br>L<br>H | 32<br>33<br>34<br>35<br>36<br>37<br>38<br>39 |

| L   | L     | н     | L<br>L L H H H H                          | L<br>H<br>H<br>L<br>H<br>H<br>H | L<br>H<br>L<br>H<br>L<br>H<br>L<br>H<br>L<br>H | 8<br>9<br>10<br>11<br>12<br>13<br>14<br>15           | н      | L    | н     | L<br>L<br>L<br>H<br>H<br>H<br>H<br>H | L<br>H<br>H<br>L<br>H<br>H  | L<br>H<br>L<br>H<br>L<br>H<br>L<br>H | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47 |

| L   | Н     | L     | L<br>L<br>H<br>H<br>H                     | L<br>H<br>H<br>L<br>H<br>H      | L<br>H<br>L<br>H<br>L<br>H                     | 16<br>17<br>18<br>19<br>20<br>21<br>22<br>23         | н<br>Н | Н    | L     | L<br>L<br>L<br>H<br>H<br>H<br>H<br>H | L<br>H<br>H<br>L<br>H<br>H  | L<br>H<br>L<br>H<br>L<br>H<br>L<br>H | 48<br>49<br>50<br>51<br>52<br>53<br>54<br>55 |

| ī   | Н     | н     | L<br>L<br>L<br>H<br>H<br>H<br>H<br>H      | L<br>H<br>H<br>L<br>H<br>H      | L<br>H<br>L<br>H<br>L<br>H<br>L<br>H           | 24<br>25<br>26<br>27<br>****<br>28<br>29<br>30<br>31 | н      | Н    | н     | L<br>L L H H H H<br>H                | L L H H L L H H             | L H L H L H                          | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63 |

\* The transmitter U 327 M radiates only commands No. 0 ... 39

\*\* Command No. 4 under address 1: Line OUT (HIGH)

\*\*\* Command No. 16 - 28 under address 1: Line IN (LOW)

### b: Address Section and Bits G, H

| Address-No. | Data<br>A1 | outp<br>A2 | ut<br>A3 | A4 | H | G |

|-------------|------------|------------|----------|----|---|---|

| 1           | Н          | L          | L        | L  | н | L |

| 2           | н          | L          | L        | н  | н | L |

| 3           | Н          | L          | н        | L  | Н | L |

| 4           | н          | L          | н        | н  | н | L |

| 5           | L          | Н          | L        | L  | L | н |

| 6           | L          | н          | L        | Н  | L | н |

| 7           | L          | ٠H         | н        | L  | L | н |

| 8           | L          | н          | н        | н  | L | Н |

| 9           | н          | Ή.         | L        | н  | X | X |

| 10          | Н          | н          | н        | L  | X | X |

| 11          | L          | L          | L        | Н  | X | X |

| 12          | L          | L          | н        | Ľ  | X | X |

| 13          | Н          | Н          | Н        | н  | X | X |

| 14          | н          | Н          | L        | L  | X | X |

| 15          | L          | L          | L        | L  | Х | X |

| 16          | L          | L          | н        | Н  | X | X |

The transmitter U 327 M sends only commands under the addresses  $1 \dots 8$ . Bits G, H are determined at the transmitter end in accordance with the above table, and can be evaluated as extra check-bits. In the case of transmitter U 328 M, for the addresses  $9 \dots 16$  bits G and H are identical with bits A2, A1.

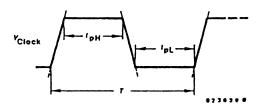

### Pin 7 Clock 4.000 MHz

Input for direct connection to a 4.000 MHz quartz crystal or for an external 4.000 MHz clock signal capacitatively coupled via C<sub>ext</sub>,

e.g. 0.1 nF (see diagram d). The clock-input handles a non-amplitudemodulated sine-wave, square wave or saw-tooth.

Diagram d For external clock supply

# Pin 8 Voltage supply $V_{DD} = 12 V \pm 10 \%$

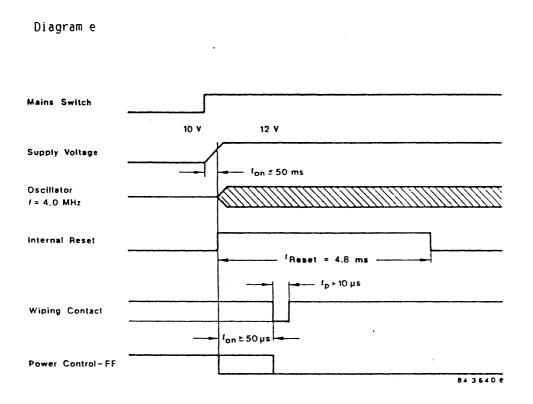

When power is applied an internal reset-signal brings the circuit to the initial condition. Simultaneously false data is prevented from appearing at the outputs. The voltage and time conditions are clear from diagram e.

| Electrical characteristics<br>Operating conditions: V <sub>DD</sub> = 10.                              |                                                                                                       |          |      |                |                 |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------|------|----------------|-----------------|

| f <sub>cl</sub> = 4.000 MHz, T <sub>amb</sub> = 0<br>unless otherwise specified                        | 85 °C,                                                                                                | Min.     | Тур. | Max.           |                 |

| Pin 8 (V <sub>DD</sub> )                                                                               |                                                                                                       |          |      |                |                 |

| Supply current<br>$V_{DD}$ = 13.2 V, T <sub>amb</sub> = 25 °C<br>$T_{amb}$ = 0 °C<br>$T_{amb}$ = 85 °C | 00 <sup>1</sup><br>00 <sup>1</sup><br>00 <sup>1</sup>                                                 |          | 22   | 40<br>46<br>30 | mA<br>mA<br>mA  |

| Pin 7 (4.000 MHz)                                                                                      |                                                                                                       |          |      |                |                 |

| Clock frequency                                                                                        | f <sub>0</sub>                                                                                        |          |      | 4.000          | MHz             |

| Clock times                                                                                            | <sup>t</sup> РН<br>t <sub>РL</sub>                                                                    | 60<br>60 |      |                | ns<br>ns        |

| External capacitive load<br>to ground (quartz drive)                                                   | с <sub>м</sub>                                                                                        | 10+      |      | 30             | pF              |

| Internal load                                                                                          | ۲                                                                                                     |          |      | 20             | рF              |

| Input leakage current<br>V <sub>I</sub> = 13.2 V                                                       | I                                                                                                     |          |      | 20             | ųА              |

| External clock drive<br>(capacitive coupling)                                                          | V <sub>clock</sub>                                                                                    | 2.0      |      | 6.0            | ۷ <sub>pp</sub> |

| direct coupling                                                                                        | V <sub>IL</sub><br>V <sub>IH</sub>                                                                    | 8.0      |      | 1.0            | V<br>V          |

| Synchron of transmitter-<br>and receiver-clock frequencies                                             | $G = \frac{1 + \frac{\Delta f_0(transm.)}{f_0(transm.)}}{1 + \frac{\Delta f_0(recvr.)}{f_0(recvr.)}}$ | 0.9995   | 1    | 1.005          |                 |

<sup>+</sup>) If the power-on rise time  $\leq$  3 ms, only.

<u>U</u> 338 M

.

|                                                                     |                                  | Min.       | Тур.       | Max.            |                                    |

|---------------------------------------------------------------------|----------------------------------|------------|------------|-----------------|------------------------------------|

| Pin 2 (IR-Signal)                                                   |                                  |            |            |                 |                                    |

| Internal capacity-coupled signal sensitivity                        |                                  |            |            |                 |                                    |

| Input voltage<br>28.8 kHz ≦ f ≦ 43.2 kHz<br>28.8 kHz ≧ f ≧ 43.2 kHz | v <sub>i</sub><br>v <sub>i</sub> | 0.5<br>0.6 | 0.7<br>0.8 | 1.1<br>1.2      | V <sub>pp</sub><br>V <sub>pp</sub> |

| Input signal compatibility                                          | v <sub>i</sub>                   |            |            | ۷ <sub>DD</sub> | V <sub>pp</sub>                    |

| Input leakage current<br>V <sub>l</sub> = 13.2 V                    | IR                               |            |            | 20              | μA                                 |

| Pin 4,5 (CS, STROBE)                                                |                                  |            |            |                 |                                    |

| Input voltages                                                      |                                  |            |            |                 |                                    |

| Normal operation:                                                   |                                  |            |            |                 |                                    |

| H-level<br>L-level                                                  | V<br>V<br>I H                    | 3.2        |            | 6.5<br>0.8      | V<br>V                             |

| Test-mode:                                                          | ۷ <sub>IL</sub>                  |            |            | 0.0             | ·                                  |

| active                                                              | ۷ <sub>IT</sub>                  | V<br>DDmir |            | ۷ <sub>DD</sub> | ۷                                  |

| Input leakage current                                               | .11                              | UUmir      | 1          | UU              |                                    |

| $V_{\rm I}$ = 13.2 V                                                | IR                               |            |            | 10              | ЦA                                 |

| Pin 6 (DATA)                                                        |                                  |            |            |                 |                                    |

| active:                                                             |                                  |            |            |                 |                                    |

| I <sub>QL</sub> = 2.0 mA                                            | VQL                              |            |            | 0.4             | ۷                                  |

| V <sub>QH</sub> = 2.4 V                                             | <sup>- 1</sup> QH                | 100        |            |                 | Αų                                 |

| Ι <sub>ΟΗ</sub> = 20 μΑ                                             | <sup>V</sup> QH                  | 3.5        |            | 7.0             | ۷                                  |

| 1 <sub>QH</sub> = 200 µA                                            | v <sub>QH</sub>                  |            |            | 5.8             | ۷                                  |

| inactive:                                                           |                                  |            |            |                 |                                    |

| V <sub>Q</sub> = 13.2 V                                             | <sup>I</sup> QR                  |            |            | 20              | μA                                 |

|                                                   |                   | Min.       | Тур.     | Max.  |    |

|---------------------------------------------------|-------------------|------------|----------|-------|----|

| Pin 3 (Test, Line) (Open drain)                   |                   |            |          |       |    |

| Test mode:                                        |                   |            |          |       |    |

| Input                                             |                   |            |          |       |    |

| H-level                                           | ۷ <sub>IH</sub>   | V<br>DDmin |          |       | ۷  |

| L-level                                           | VIL               | UUMIN      |          | 0.8   | V  |

| Output                                            |                   |            |          |       |    |

| I <sub>OL</sub> = 2.0 mA                          | V <sub>QL</sub>   |            |          | 0.8   | ۷  |

| $V_{Q} = 13.2 V$                                  | I QR              |            |          | 20    | μA |

| Normal operation:                                 |                   |            |          |       |    |

| Input with wiping contact                         |                   |            |          |       |    |

| Reset Line V <sub>IH</sub> = 4.0 V                | I <sup>+</sup>    |            |          | 50    | mΑ |

| Set Line $V_{IL} = 0.8 V$                         | I <sup>+</sup>    |            |          | 100   | μA |

| Output                                            |                   |            |          |       |    |

| I <sub>QL</sub> = 2.0 mA                          | V <sub>QL</sub>   |            |          | 0.8   | ۷  |

| $V_{Q} = 13.2 V$                                  | IQR               |            |          | 20    | μA |

| I <sup>+</sup> = Changeover current for t ≦ 10 µs |                   |            |          |       |    |

| Times Pin 4, 5, 6 (CS, STROBE, DATA)              |                   |            |          |       |    |

| C <sub>1</sub> = 100 pF                           | <sup>t</sup> csd  |            | 1.5      | 2.5   | μs |

| -                                                 | t <sub>STL</sub>  | 1          |          | 100   | μs |

|                                                   | t <sub>STH</sub>  | 1          |          |       | μs |

|                                                   | <sup>t</sup> STDA |            | 1.5      | 2.5   | μs |

|                                                   | <sup>t</sup> DCS  | •          |          | 2     | μs |

|                                                   | <sup>t</sup> stde | 0          |          |       | μs |

|                                                   | tcs               | 2          |          |       | μs |

|                                                   | t <sub>cst</sub>  |            |          | 400   | μs |

| The times refer to an L-level of 0.8 V (T         | S. STROBE), or    | • 0 4 V (  | DATA) ar | nd an |    |

The times refer to an L-level of 0.8 V (CS, STROBE), or 0.4 V (DATA) and an H-level of 3.2 V (CS, STROBE), or 2.4 V (DATA).

.

.