## MOTOROLA SEMICONDUCTOR TECHNICAL DATA

MC33120

# **Subscriber Loop Interface Circuit**

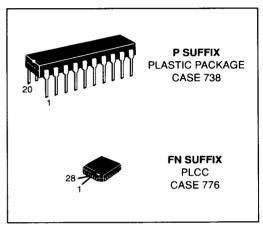

The MC33120 is designed to provide the interface between the 4-wire side of a central office, or PBX, and the 2-wire subscriber line. Interface functions include battery feed, proper loop termination AC impedance, hookswitch detection, adjustable transmit, receive, and transhybrid gains, and single/double fault indication. Additionally the MC33120 provides a minimum of 58 dB of longitudinal balance (4-wire and 2-wire).

The transmit and receive signals are referenced to analog ground, while digital signals are referenced to digital ground, easing the interface to codecs, filters, etc. The 2 status outputs (hookswitch and faults) and the Power Down Input are TTL/CMOS compatible. The Power Down Input permits local shutdown of the circuit.

Internal drivers allow the external loop current pass transistors to be standard bipolar transistors (non-Darlington).

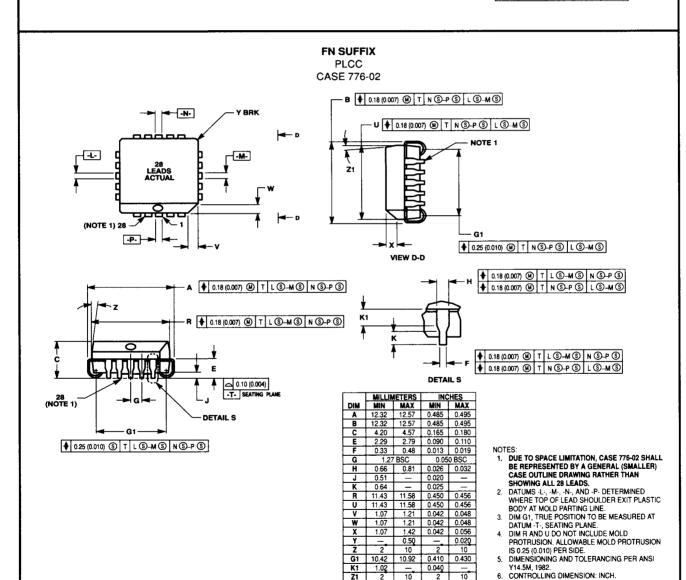

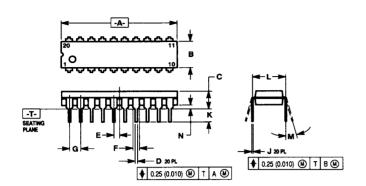

The MC33120 is available in a 20 pin DIP and a 28 pin PLCC surface mount package.

- 58 dB Longitudinal Balance Guaranteed; 4-wire and 2-wire

- Transmit, Receive, and Transhybrid Gains Externally Adjustable

- Return Loss Externally Adjustable

- Proper Hookswitch Detection With 30  $k\Omega$  Leakage

- Single/Double Fault Indication With Shutdown for Thermal Protection

- Critical Sense Resistors Included Internally

- Standard Power Supplies: 42 V to 58 V, and +5.0 V, ±10%

- On-Hook Transmission

- Power Down Input (TTL and CMOS Compatible)

- Operating Ambient Temperature: 40°C to +85°C

- Available in a 20 Pin DIP and 28 Pin PLCC Package

## SUBSCRIBER LOOP INTERFACE CIRCUIT (SLIC)

THIN FILM

SILICON MONOLITHIC

INTEGRATED CIRCUIT

| ORDERING INFORMATION             |                |             |  |  |  |

|----------------------------------|----------------|-------------|--|--|--|

| Temperature Device Range Package |                |             |  |  |  |

| MC33120P                         | 400 45 . 0500  | Plastic DIP |  |  |  |

| MC33120FN                        | – 40° to +85°C | PLCC        |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                                                                 | Symbol           | Value                     | Unit |

|--------------------------------------------------------------------------------|------------------|---------------------------|------|

| Supply Voltage with respect to V <sub>CC</sub> with respect to V <sub>DG</sub> | VEE<br>VDD       | - 60, +0.5<br>- 0.5, +7.0 | Vdc  |

| Input Voltage @ PDI, with respect to V <sub>DG</sub> @ Pins 1–5, 16–20         | V <sub>in</sub>  | - 0.5, +7.0<br>VEE to VCC | Vdc  |

| Storage Temperature Range                                                      | T <sub>stg</sub> | - 65 to +150              | °C   |

| Junction Temperature                                                           | TJ               | 150                       | ô    |

Devices should not be operated at these values. The "Recommended Operating Conditions" table provides conditions for actual device operation.

## **RECOMMENDED OPERATING CONDITIONS**

| Characteristic                                                                       | Symbol                             | Min                     | Тур          | Max                | Unit |

|--------------------------------------------------------------------------------------|------------------------------------|-------------------------|--------------|--------------------|------|

| Supply Voltage (with respect to V <sub>CC</sub> ) (with respect to V <sub>DG</sub> ) | VEE<br>V <sub>DD</sub>             | - 58<br>+4.5            | - 48<br>+5.0 | – 42<br>+5.5       | Vdc  |

| (with respect to $V_{CC}$ ) (with respect to $V_{CC}$ ) (with respect to $V_{AG}$ )  | VAG<br>VDG                         | - 3.0<br>- 3.0<br>- 3.0 | 0<br>0<br>0  | +10<br>+7.0<br>+10 | Vdc  |

| (with respect to $V_{EE}$ ) (with respect to $V_{CC}$ and $V_{AG}$ )                 | V <sub>DD</sub>                    | +3.5                    | <del>-</del> | +63.5              | Vdc  |

| Loop Current                                                                         | ILOOP                              | 15                      | _            | 50                 | mA   |

| PDI Input Voltage                                                                    | V <sub>PDI</sub>                   | 0                       | _            | V <sub>DD</sub>    | Vdc  |

| Sink Current<br>ST1<br>ST2                                                           | IST1L<br>IST2L                     | 0                       | _            | 1.0<br>1.0         | mA   |

| Transmit Signal Level at Tip & Ring<br>Receive Signal Level at V <sub>RX</sub>       | S <sub>TX</sub><br>S <sub>RX</sub> | 48<br>48                | _            | +3.0<br>+3.0       | dBm  |

| Loop Resistance                                                                      | RL                                 | 0                       | _            | 2.0                | kΩ   |

| External Transistor Beta                                                             | H <sub>FE</sub>                    | 40                      | _            | 500                | A/A  |

| Operating Ambient Temperature (See text for derating)                                | TA                                 | - 40                    | -            | +85                | °C   |

All limits are not necessarily functional concurrently.

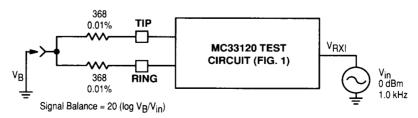

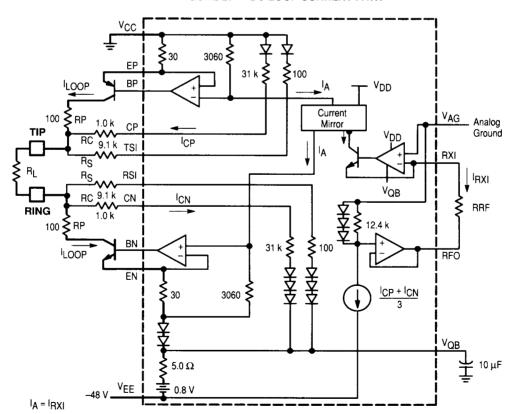

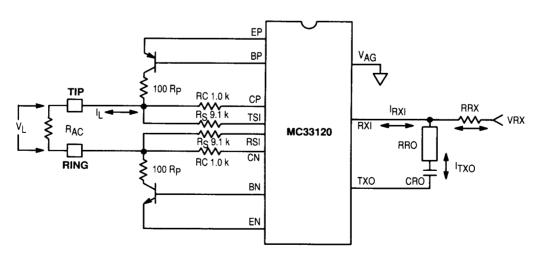

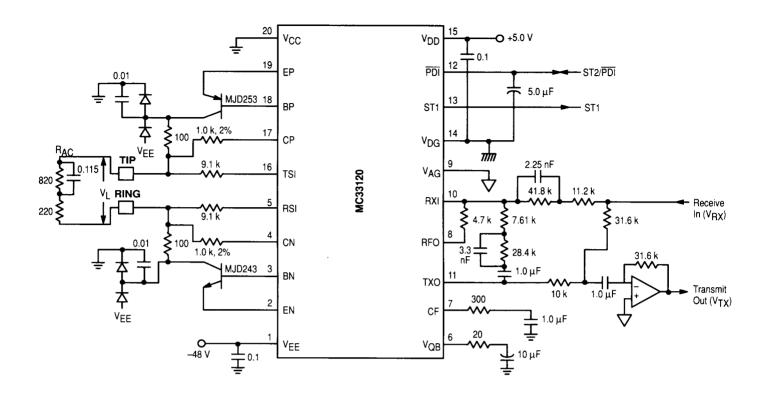

# **ELECTRICAL CHARACTERISTICS** ( $V_{EE} = -48 \text{ V}$ , $V_{DD} = +5.0 \text{ V}$ , unless otherwise noted, $V_{CC} = V_{AG} = V_{DG} = 0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ , see Figure 1, unless otherwised noted.)

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Symbol                       | Min                      | Тур                         | Max                   | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------|-----------------------------|-----------------------|------|

| POWER SUPPLIES                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |                          |                             |                       |      |

| $\begin{split} &V_{\mbox{\footnotesize{EE}}}\mbox{Current}\\ &\mbox{On Hook }(R_L>10\mbox{ M}\Omega,V_{\mbox{\footnotesize{EE}}}=-58\mbox{ V})\\ &\mbox{Off Hook }(R_L=0\Omega,V_{\mbox{\footnotesize{EE}}}=-58\mbox{ V})^{\star}\\ &\mbox{V}_{\mbox{\footnotesize{DD}}}\mbox{Current}\\ &\mbox{On Hook }(R_L>10\mbox{ M}\Omega,V_{\mbox{\footnotesize{DD}}}=+5.5\mbox{ V})\\ &\mbox{Off Hook }(R_L=0\Omega,V_{\mbox{\footnotesize{DD}}}=+5.5\mbox{ V}) \end{split}$ | IEEN<br>IEEF<br>IDDN<br>IDDF | - 2.7<br>- 75<br><br>5.5 | - 1.2<br>- 58<br>1.4<br>9.0 | <br>- 45<br>2.7<br>15 | mA   |

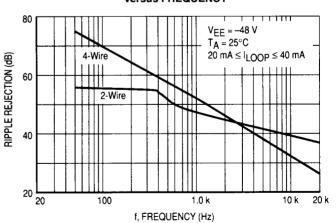

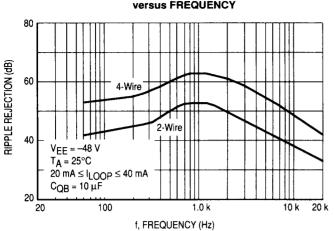

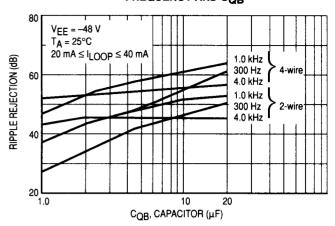

| $V_{EE}$ Ripple Rejection $f = 1.0 \text{ kHz}$ , at $V_{TX}$ (4-wire) $f = 1.0 \text{ kHz}$ , at Tip/Ring (2-wire) $V_{DD}$ Ripple Rejection $f = 1.0 \text{ kHz}$ , at $V_{TX}$ (4-wire) $f = 1.0 \text{ kHz}$ , at Tip/Ring (2-wire)                                                                                                                                                                                                                              | PSRR                         | 40<br>40<br>37<br>37     | 62<br>52<br>52<br>48        | <br>                  | dB   |

\*Includes loop current.

**ELECTRICAL CHARACTERISTICS** ( $V_{EE} = -48 \text{ V}, V_{DD} = +5.0 \text{ V}, \text{unless otherwise noted}, V_{CC} = V_{AG} = V_{DG}, T_A = 25 ^{\circ}\text{C}, \text{ see Figure 1}$

| Characteristic                                                                                                                                                                          | Symbol                             | Min            | Тур            | Max           | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|---------------|------|

| LOOP FUNCTIONS                                                                                                                                                                          |                                    |                |                |               |      |

| Loop Current<br>Maximum (RRF = 4.7 k, R <sub>L</sub> = 10 $\Omega$ )<br>Nominal (RRF = 4.7 k, R <sub>L</sub> = 600 $\Omega$ )<br>Minimum (RRF = 4.7 k, R <sub>L</sub> = 1800 $\Omega$ ) | ILMAX<br>ILOOP<br>ILMN             | 41<br>37<br>19 | 43<br>40<br>21 | 53<br>48<br>— | mA   |

| Battery Feed Resistance (RRF = 4.7 k, R <sub>L</sub> = 1800 Ω)*                                                                                                                         | R <sub>BF</sub>                    | 475            | 508            | 675           | Ω    |

| Hookswitch Threshold<br>On-to-Off Hook<br>Off-to-On Hook                                                                                                                                | R <sub>NF</sub><br>R <sub>FN</sub> | 2.0            | 3.1<br>7.0     | <u> </u>      | kΩ   |

| Fault Detection Threshold<br>Ring-to-Ground (R <sub>L</sub> = 600 $\Omega$ )<br>Tip-to-Battery (R <sub>L</sub> = 600 $\Omega$ )                                                         | R <sub>RG</sub><br>R <sub>TB</sub> | 600<br>600     | 660<br>660     | _             | Ω    |

<sup>\*</sup>Calculated from [(48/I<sub>LMN</sub>) - 1800]

#### **GAIN LEVELS**

| Transmit Voltage Gain (CP, CN to TXO)                                                                                                                                                                                                                                                               | G <sub>TX1</sub>  | _                        | 0.328                     | _                     | V/V   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|---------------------------|-----------------------|-------|

| Transmit Voltage Gain $(V_{TX}/V_L)$<br>$V_L = 0$ dBm, $f = 1.0$ kHz, $V_L = 0$ dBm, $f = 3.4$ kHz, with respect to $V_L = 0$ dBm, $V_L = 0$ dBm, $V_L = 0$ dBm, $V_L = 0$ kHz, with respect to $V_L = 0$ dBm, $V_L = 0$ dBm, $V_L = 0$ kHz, with respect to $V_L = 0$ dBm, $V_L = 0$               | G <sub>TX2</sub>  | - 0.3<br>- 0.1<br>- 0.15 | 0.0<br>0.0<br>0.0<br>±0.1 | +0.3<br>+0.1<br>+0.15 | dB    |

| Transmit Distortion (at Pin 11)<br>$(f = 300 \text{ Hz to } 4.0 \text{ kHz}, -40 \text{ dBm} \le V_{T-R} \le +5.0 \text{ dBm})$                                                                                                                                                                     | THDT              | _                        | 0.05                      | _                     | %     |

| Receive Current Gain (IEP/IRXI)                                                                                                                                                                                                                                                                     | G <sub>RX1</sub>  | 94                       | 102                       | 110                   | mA/mA |

| Receive Voltage Gain ( $V_L/V_{RXI}$ ) ( $R_L = 600 \Omega$ )<br>$V_{RXI} = 0$ dBm, $f = 1.0$ kHz<br>$V_{RXI} = 0$ dBm, $f = 3.4$ kHz, with respect to $G_{RX2}$<br>$V_{RXI} = +3.0$ dBm, $f = 1.0$ kHz, with respect to $G_{RX2}$<br>$V_{RXI} = -48$ dBm, $f = 1.0$ kHz, with respect to $G_{RX2}$ | G <sub>RX2</sub>  | - 0.3<br>- 0.1<br>- 0.15 | 0.0<br>0.0<br>0.0<br>±0.1 | +0.3<br>+0.1<br>+0.15 | dB    |

| Receive Distortion (f = 300 Hz to 4.0 kHz, $-$ 40 dBm $\leq$ V <sub>RXI</sub> $\leq$ +5.0 dBm)                                                                                                                                                                                                      | THDR              | _                        | 0.05                      | _                     | %     |

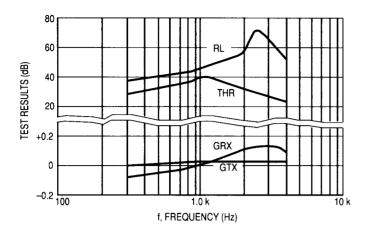

| Return Loss (Reference = 600 Ω resistive, f = 1.0 kHz)                                                                                                                                                                                                                                              | RL                | 30                       | >40                       | _                     | dB    |

| Transhybrid Rejection (R <sub>L</sub> = 600 Ω, f = 1.0 kHz, Figure 4)                                                                                                                                                                                                                               | THR               | _                        | 44                        | _                     | dB    |

| ONGITUDINAL SIGNALS (V <sub>CM</sub> = 5.12 Vrms, see Figures 1 and 2)                                                                                                                                                                                                                              |                   |                          |                           |                       |       |

| 2-Wire Balance, f = 1.0 kHz, $Z_{aC}$ = 600 $\Omega$ (@ Tip/Ring) 4-Wire Balance, f = 1.0 kHz, $Z_{aC}$ = 600 $\Omega$ (@ $V_{TX}$ )                                                                                                                                                                | LB                | 58<br>58                 | 64<br>64                  | _                     | dB    |

| 2-Wire Balance, f = 330 Hz, $Z_{ac}$ = 600 $\Omega$ (@ Tip/Ring)<br>4-Wire Balance, f = 330 Hz, $Z_{ac}$ = 600 $\Omega$ (@ V <sub>TX</sub> )                                                                                                                                                        |                   | 58<br>58                 | 64<br>64                  | _                     |       |

| 2-Wire Balance, f = 3.3 kHz, $Z_{ac}$ = 600 $\Omega$ (@ Tip/Ring) 4-Wire Balance, f = 3.3 kHz, $Z_{ac}$ = 600 $\Omega$ (@ $V_{TX}$ )                                                                                                                                                                |                   | 53<br>53                 | 60<br>60                  |                       |       |

| 2-Wire Balance, f = 1.0 kHz, $Z_{ac}$ = 900 $\Omega$ (@ Tip/Ring)<br>4-Wire Balance, f = 1.0 kHz, $Z_{ac}$ = 900 $\Omega$ (@ $V_{TX}$ )                                                                                                                                                             |                   | _                        | 62<br>62                  | _                     |       |

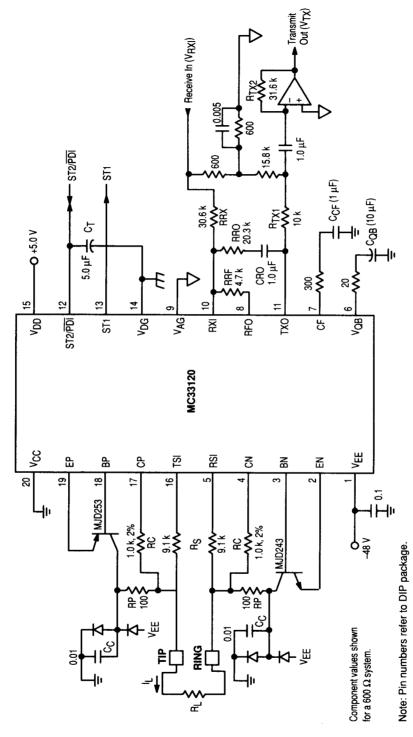

| Signal Balance, f = 1.0 kHz (Figure 3)                                                                                                                                                                                                                                                              |                   | 40                       | 55                        | _                     |       |

| Longitudinal Impedance, RS = 9100 $\Omega$                                                                                                                                                                                                                                                          | Z <sub>LONG</sub> | 150                      | 180                       | 210                   | Ω     |

| Maximum Longitudinal Current per side<br>f = 1.0 kHz, $I_{LOOP} = I_{LMN}$ , $C_T = 0.1 \mu F$                                                                                                                                                                                                      | l <sub>L</sub> M  | 8.5                      | 16                        | _                     | mA    |

#

| Ohamatariatia                                                                                                                                           | Cumbat                                 | A4im                   | T              | Man                    | I I mid       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------|----------------|------------------------|---------------|

| Characteristic                                                                                                                                          | Symbol                                 | Min                    | Тур            | Max                    | Unit          |

| LOGIC INTERFACE                                                                                                                                         | ,                                      |                        | 1              | 1                      | , , ,         |

| ST1 Output Voltage<br>Low ( $I_{ST1}$ = 1.0 mA, $V_{DD}$ = 5.5 V)<br>High ( $I_{ST1}$ = - 100 $\mu$ A, $V_{DD}$ = 4.5 V)                                | VOL<br>VOH                             | V <sub>DG</sub><br>2.4 | 0.17<br>3.2    | 0.4<br>                | Vdc           |

| ST2 Output Voltage<br>Low ( $I_{ST2}$ = 1.0 mA, $V_{DD}$ = 5.5 V)<br>High ( $I_{ST2}$ = - 100 $\mu$ A, $V_{DD}$ = 4.5 V)                                | V <sub>OL</sub><br>VOH                 | V <sub>DG</sub>        | 0.17<br>4.3    | 0.4                    |               |

| Time Delay  Hookswitch Closure to ST1 Change  Hookswitch Opening to ST1 Change                                                                          | <sup>t</sup> ST11<br><sup>t</sup> ST12 |                        | 10<br>200      | _                      | μѕ            |

| Hookswitch Closure to 90% of Loop Current ( $C_T = 0.1 \mu F$ )                                                                                         | tHS                                    | _                      | 19             | _                      | ms            |

| PDI Taken High-to-Low to 10% of Loop Current PDI Taken Low-to-High to 90% of Loop Current                                                               | <sup>†</sup> ST21<br><sup>†</sup> ST22 | _                      | 18<br>10       | _                      | ms<br>μs      |

| PDI Input Current $V_{PDI} = 3.0 \text{ V}, R_L = 600 \Omega, V_{DD} = 5.0 \text{ V}$ $V_{PDI} = 0 \text{ V}, R_L = 600 \Omega, V_{DD} = 5.5 \text{ V}$ | ΊΗ                                     | - 1250<br>             | - 800<br>- 800 | - 300<br>—             | μА            |

| PDI Input Voltage<br>Low<br>High                                                                                                                        | V <sub>IL</sub><br>VIH                 | V <sub>DG</sub>        | _              | 0.8<br>V <sub>DD</sub> | V             |

| MISCELLANEOUS                                                                                                                                           | •                                      |                        |                |                        | -             |

| V <sub>QB</sub> Voltage (V <sub>QB</sub> – V <sub>EE</sub> )<br>@ I <sub>L</sub> = 20 mA<br>@ I <sub>L</sub> = 40 mA                                    | V <sub>QB</sub>                        | _                      | 0.82<br>0.95   | _                      | Vdc           |

| TXO Offset Voltage ( $V_{TXO} - V_{AG}$ ) @ $R_L = 600 \Omega$                                                                                          | V <sub>TXO</sub>                       | - 400                  | +30            | +400                   | mVdc          |

| TXO Output Current                                                                                                                                      | I <sub>TXO</sub>                       | ±275                   | ±800           |                        | μ <b>A</b> pk |

| RXI Offset Voltage ( $V_{RXI} - V_{AG}$ ) @ $R_L = 600 \Omega$                                                                                          | VRXOS                                  |                        | 0.8            | _                      | mVdc          |

| V <sub>AG</sub> Input Current @ R <sub>L</sub> = 600 Ω                                                                                                  | lvag                                   | <u> </u>               | 0.2            | _                      | μΑ            |

| Idle Channel Noise (with C-message filter, $R_L$ = 600 $\Omega$ ) @ TXO (Pin 11) @ Tip/Ring                                                             | NIC4<br>NIC2                           | _<br>_                 | - 10<br>- 5.0  | _                      | dBrnc         |

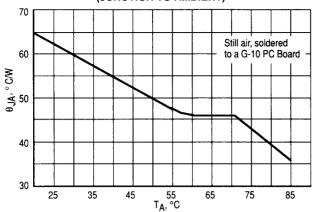

| Thermal Resistance — Junction to Ambient (Either package, in still air, soldered to a PC board) (@ T <sub>A</sub> = +25°C) (@ T <sub>A</sub> = +85°C)   | θJA                                    |                        | 62<br>36       | _                      | °C/W          |

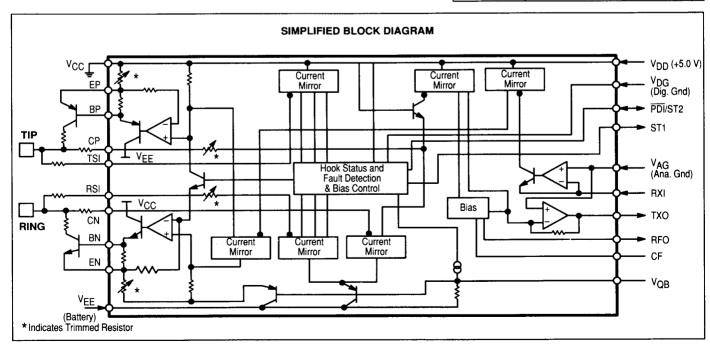

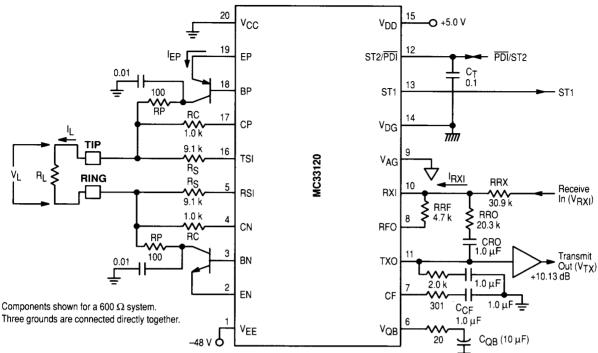

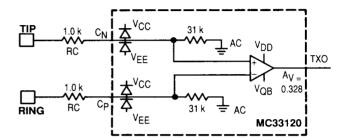

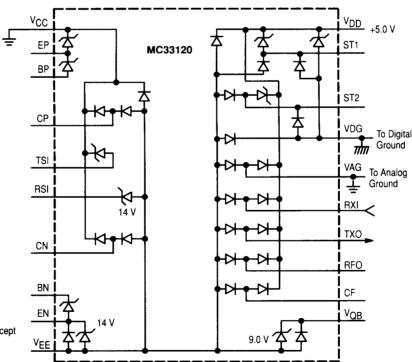

#### FIGURE 1 — TEST CIRCUIT

Note: Pin numbers refer to DIP package.

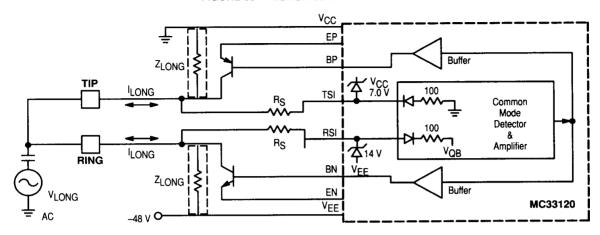

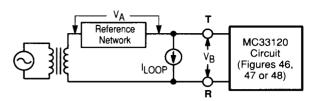

FIGURE 2 — LONGITUDINAL BALANCE TEST

(Per IEEE-455)

368

0.01%

TIP

MC33120 TEST

CIRCUIT (FIG. 1)

4-Wire Balance = 20 (log V<sub>4</sub>/V<sub>CM</sub>)

2-Wire Balance = 20 (log V<sub>2</sub>/V<sub>CM</sub>)

Amplifier

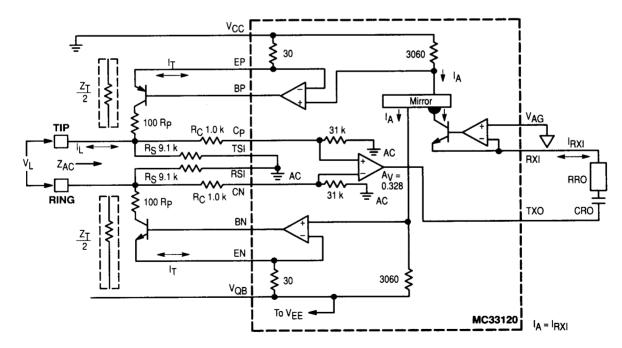

FIGURE 3 — SIGNAL BALANCE TEST

Note: Pin numbers refer to DIP package.

## PIN DESCRIPTION

|                 | Pin |      |                                                                                                                                                                                                                                                                |

|-----------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | DIP | PLCC | Description                                                                                                                                                                                                                                                    |

| VCC             | 20  | 28   | Connect to noise-free Battery ground. Carries loop current and some bias currents.                                                                                                                                                                             |

| EP              | 19  | 27   | Connect to the emitter of the PNP pass transistor.                                                                                                                                                                                                             |

| BP              | 18  | 26   | Connect to the base of the PNP pass transistor.                                                                                                                                                                                                                |

| СР              | 17  | 24   | Connect to TIP through a current limiting protection resistor (R <sub>C</sub> ). CP is the noninverting input to the internal transmit amplifier (Figure 28). Input impedance is 31 k $\Omega$ .                                                               |

| TSI             | 16  | 23   | Sense input. Connect to TIP through a current limiting protection resistor (R <sub>S</sub> ) which also sets the longitudinal impedance. Input impedance is ≈100 Ω to V <sub>CC</sub> .                                                                        |

| V <sub>DD</sub> | 15  | 22   | Connect to a +5.0 V, ±10% supply, referenced to digital ground. Powers logic section and provides some bias currents for the loop current drivers.                                                                                                             |

| V <sub>DG</sub> | 14  | 20   | Digital Ground. Reference for ST1, ST2 and V <sub>DD</sub> . Connect to system digital ground.                                                                                                                                                                 |

| ST1             | 13  | 18   | Status Output (TTL/CMOS). Indicates hook switch status — High when on-hook, low when off-hook, and pulse dialing information. Used with ST2 to indicate fault conditions.                                                                                      |

| ST2/PDI         | 12  | 17   | Status output <b>and</b> an input (TTL/CMOS). As an output, ST2 can indicate hook status — Low when on-hook, high when off-hook. Used with ST1 to indicate fault conditions. As an input, it can be taken low (when off-hook) to deny subscriber loop current. |

| TXO             | 11  | 16   | Transmit voltage output. Amplitude is ≈1/3 that across CP and CN. Nominally capable of 800 μA output current. DC referenced to V <sub>AG</sub> .                                                                                                               |

| RXI             | 10  | 14   | Receive current input. Current at this pin is multiplied by 102 at EP and EN to generate loop current. RXI is a virtual ground at V <sub>AG</sub> level. Current flow is <b>out</b> of this pin.                                                               |

| V <sub>AG</sub> | 9   | 13   | Analog ground, reference for TXO and RXI. Connect to system analog ground.                                                                                                                                                                                     |

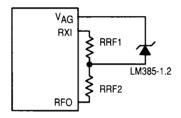

| RFO             | 8   | 12   | A resistor between this pin and RXI sets the maximum loop current and DC feed resistance. Minimum resistor value is 3.3 k (see Figures 5–7).                                                                                                                   |

| CF              | 7   | 10   | A low leakage capacitor between this pin and V <sub>AG</sub> provides DC and AC signal separation. A series resistor is required for battery supply turn-on/off transient protection (Figure 4).                                                               |

| V <sub>QB</sub> | 6   | 8    | Quiet Battery. A capacitor between VQB and VCC filters noise and ripple from VEE, providing a quiet battery source for the speech amplifiers. A series resistor is required for battery supply turn-on/off transient protection (Figure 4).                    |

| RSI             | 5   | 7    | Sense input. Connect to RING through a current limiting protection resistor which also sets the longitudinal impedance. Input impedance is $\approx 100~\Omega$ to VQB.                                                                                        |

| CN              | 4   | 6    | Connect to RING through a current limiting protection resistor. CN is the inverting input to the internal transmit amplifier (Figure 28). Input impedance is 31 k $\Omega$ .                                                                                   |

| BN              | 3   | 4    | Connect to the base of the NPN pass transistor.                                                                                                                                                                                                                |

| EN              | 2   | 3    | Connect to the emitter of the NPN pass transistor.                                                                                                                                                                                                             |

| VEE             | 1   | 2    | Connect to battery voltage. Nominally – 48 V, it can range from – 42 to – 58 V.                                                                                                                                                                                |

(Pins 1, 5, 9, 11, 15, 19, 21, and 25 are not internally connected on the PLCC package).

MOTOROLA 7 MC33120

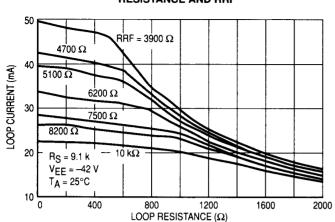

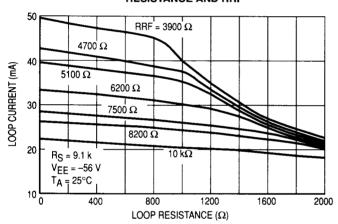

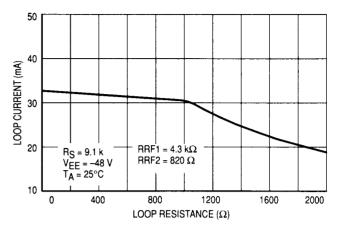

#### FIGURE 5 — LOOP CURRENT versus LOOP **RESISTANCE AND RRF**

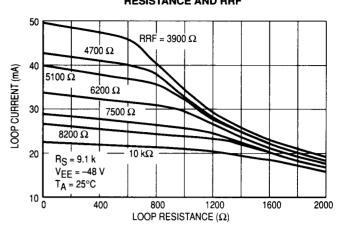

#### FIGURE 6 — LOOP CURRENT versus LOOP **RESISTANCE AND RRF**

FIGURE 7 — LOOP CURRENT versus LOOP RESISTANCE AND RRF

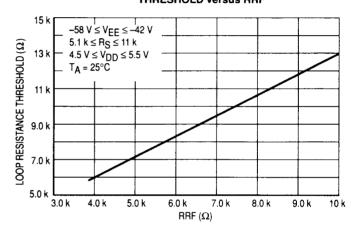

FIGURE 8 — OFF-HOOK TO ON-HOOK **THRESHOLD versus RRF**

FIGURE 9 --- ON-HOOK TO OFF-HOOK THRESHOLD versus RS

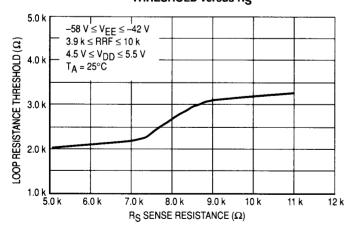

FIGURE 10 —  $I_{DD}$  versus LOOP CURRENT

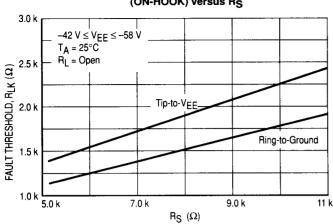

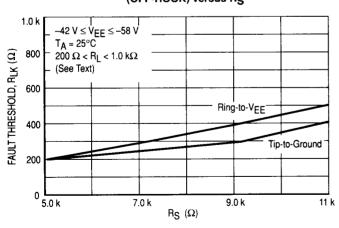

## FIGURE 11 — FAULT THRESHOLD (ON-HOOK) versus R<sub>S</sub>

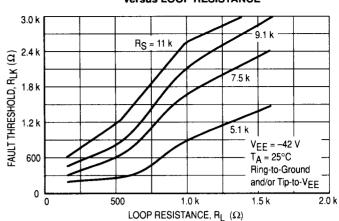

# FIGURE 12 — FAULT THRESHOLD (OFF-HOOK) versus LOOP RESISTANCE

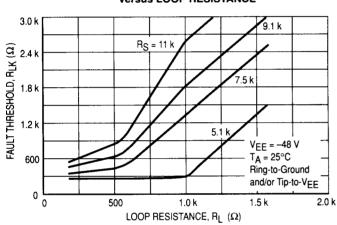

FIGURE 13 — FAULT THRESHOLD (OFF-HOOK) versus LOOP RESISTANCE

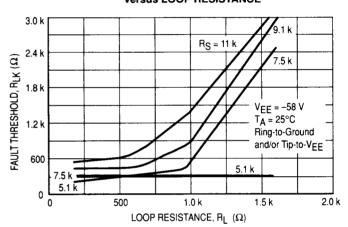

FIGURE 14 — FAULT THRESHOLD (OFF-HOOK)

versus LOOP RESISTANCE

FIGURE 15 — FAULT THRESHOLD (OFF-HOOK) versus R<sub>S</sub>

FIGURE 16 — V<sub>DD</sub> RIPPLE REJECTION versus FREQUENCY

# FIGURE 17 — V<sub>EE</sub> RIPPLE REJECTION versus FREQUENCY

# FIGURE 18 — $V_{\mbox{\scriptsize EE}}$ RIPPLE REJECTION versus FREQUENCY AND $C_{\mbox{\scriptsize QB}}$

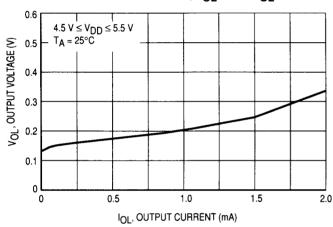

FIGURE 19 — ST1, VOL versus IOL

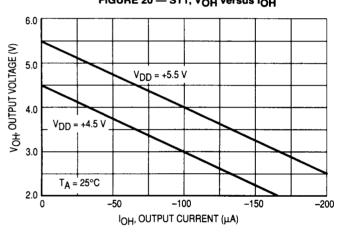

FIGURE 20 — ST1, V<sub>OH</sub> versus I<sub>OH</sub>

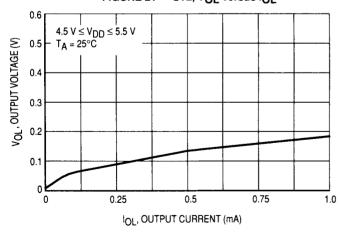

FIGURE 21 — ST2, V<sub>OL</sub> versus I<sub>OL</sub>

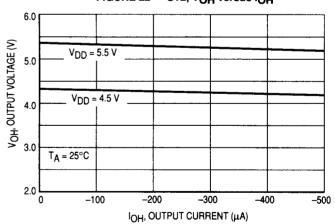

FIGURE 22 — ST2,  $V_{\mbox{OH}}$  versus  $I_{\mbox{OH}}$

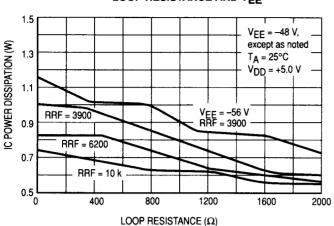

## FIGURE 23 — IC POWER DISSIPATION versus LOOP RESISTANCE AND VEE

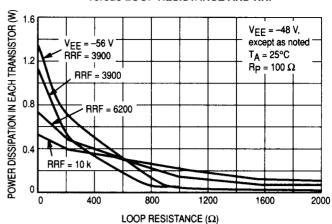

#### FIGURE 24 — TRANSISTOR POWER DISSIPATION versus LOOP RESISTANCE AND RRF

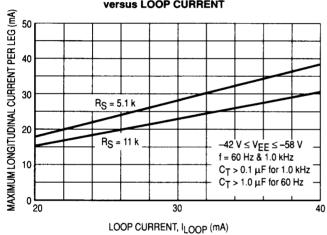

#### FIGURE 25 — MAXIMUM LONGITUDINAL CURRENT versus LOOP CURRENT

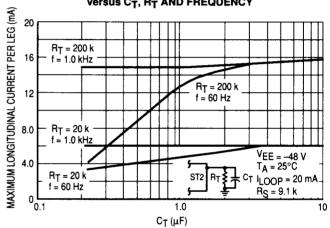

#### FIGURE 26 - MAXIMUM LONGITUDINAL CURRENT versus CT, RT AND FREQUENCY

#### **FUNCTIONAL DESCRIPTION**

#### Introduction

The MC33120 is a solid state SLIC (Subscriber Line Interface Circuit) which provides the interface between the two wire telephone line and the four wire side of a Central Office or PBX. Most of the BORSCHT functions are provided, specifically:

- Battery feed of the loop current to the line, with programmable maximum current for short lines and battery feed resistance for long lines.

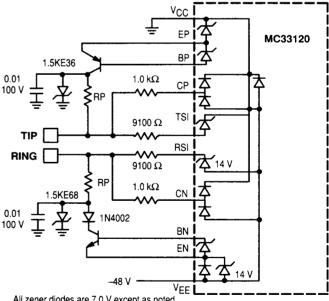

- Overvoltage protection through internal clamp diodes and external resistors and diodes.

- Supervision, in that hook status is indicated in the presence of ≥30 kΩ leakage, and regardless of whether or not the circuit is powered down intentionally by the Central Office or PBX. Fault conditions are detected and indicated to the system. Dialing (pulse and DTMF) information is passed through the MC33120 to the 4-wire side.

- Hybrid function, in that the MC33120 is a 2-to-4 wire converter. Transmit, receive, return loss, and transhybrid gains are independently adjustable.

The MC33120 does not provide ring insertion, ring trip, digital coding/decoding of the speech signals, nor test functions. These must be provided external to this device.

The MC33120 controls two external transistors (one NPN and one PNP) through which the loop current flows. By appropriate circuit design, the power dissipation (which can exceed 3.0 watts under certain worst case conditions) is

approximately equally distributed among the two transistors and the IC, thereby lowering junction temperatures and increasing long term reliability. In most situations, heatsinks will not be required.

The MC33120 incorporates critical sense resistors internally, which are trimmed for optimum performance. With this technique, the external resistors on the two wire side, which generally must be high wattage for transient protection reasons, can be non-precision.

Longitudinal balance is tested to a minimum of 58 dB @ 1.0 kHz (refer to Electrical Characteristics and Figure 1) for both the two wire and four wire side, and typically measures in the mid-60s. The longitudinal current capability is tested to a minimum of 8.5 mArms per side (refer to Electrical Characteristics and Figure 1) at a loop current of 20 mA.

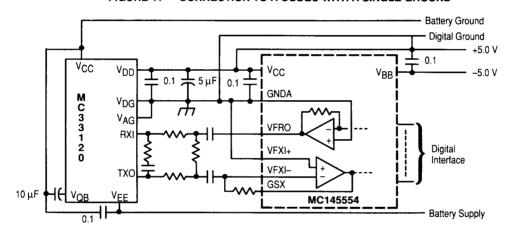

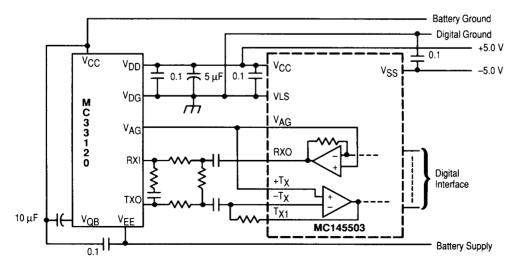

Following is a description of the individual sections. Figure 4 is the reference schematic.

#### **DC Loop Current**

The DC loop current is determined by the battery voltage ( $V_{EE}$ ), the load resistance across Tip and Ring, and the resistor at RFO. Varying the 4 resistors R<sub>S</sub> and RC will influence the loop current a small amount (<5%). The curves of Figures 5–7 indicate the loop current versus loop resistance, different values of RRF, and for various values of V<sub>EE</sub>. The graphs represent performance at T<sub>A</sub> = 25°C and after the IC had reached a steady state temperature (>5 minutes).

FIGURE 27 — DC LOOP CURRENT PATH

Figure 27 is representative of the DC loop current path (bold lines). On a long line ( $R_1 > 1.0 \text{ k}\Omega$ ), the loop current can be determined from the following equation:

$$I_{LOOP} = \frac{(|V_{EE}| - 3.6 \text{ V}) \cdot 13}{RRF + \{(R_L + 5) \cdot 13\}}$$

(Equation 1)

On short lines (R<sub>1</sub> < 1.0 k $\Omega$ ), the three diodes across the 12.4 k resistor clamp the voltage at RFO, thereby preventing the RXI current from increasing as the load resistance is decreased. The maximum loop current is:

$$I_{LOOP \text{ (MAX)}} = \frac{1.85 \text{ V} \cdot 102}{\text{BBF}} (T_{A} = 25^{\circ}\text{C}) \text{ (Equation 2)}$$

Due to the temperature dependence of a diode's forward voltage, the maximum loop current will change with temperature by  $\approx -0.3\%$ /°C.

The battery feed resistance ( $\Delta V_{TIP}/\Delta I_I$ ) is  $\approx 400 \Omega$ , but depends on the loop current, VEE, RRF, and is a valid parameter only on long lines where the current limit is not in effect. On short lines, the feed resistance is high since the loop current is clamped at a constant level. The AC impedance (Return Loss) however, is not determined nor affected by the DC parameters. See the Applications Section for Return Loss information.

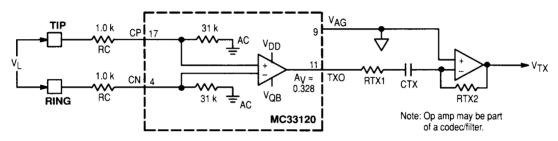

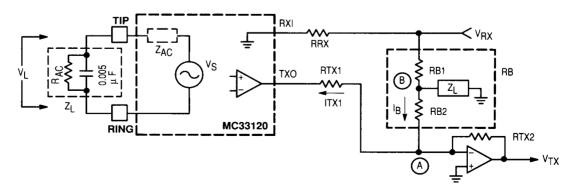

#### **Transmit Path**

The transmit path, shown in Figure 28, consists of an internal amplifier which has inputs at CP and CN, and its output at TXO. The gain is internally fixed at 0.328 V/V (-9.7 dB). The output is in phase with the signal at CP (normally the same as TIP), and is out of phase with the signal at CN. The signal at TXO is also out of phase with that at V<sub>RX</sub>, the receive signal input, described in another

#### FIGURE 28 — TRANSMIT PATH

The TXO output can swing ≈3.0 Vp-p, with a nominal current capability of ±800 µA peak (±275 µA minimum). The load on TXO is the parallel combination of RTX1 and the RRO network (described later). TXO is nominally internally biased at the VAG DC level, but has an offset which varies with loop current.

In normal applications, the signal at CP/CN is reduced slightly from that at Tip/Ring by the voltage divider composed of the external RC resistors, and the internal 31 k resistors. The value of the RC resistors depends on the transient protection needed, described in another section, with 1.0 k $\Omega$ resistors being suitable for most applications. The resulting signal at TXO needs to be gained up to obtain 0 dB from Tip/Ring to  $V_{TX}$  (the 4-wire output). The common method involves an external op amp, as shown in Figure 28, with a gain of RTX2/RTX1. The gain from  $V_{\mbox{\scriptsize L}}$  to  $V_{\mbox{\scriptsize TX}}$  is:

$$\frac{V_{TX}}{V_L} = \frac{RTX2 \cdot 31 \text{ k} \cdot 0.328}{RTX1 \cdot (RC + 31 \text{ k})}$$

(Equation 3)

If a codec/filter is used, many of which include an internal op amp, a separate op amp is not needed. CTX is primarily for DC blocking (of the TXO offset), and is usually large (1.0 μF) so as to not affect the gain.

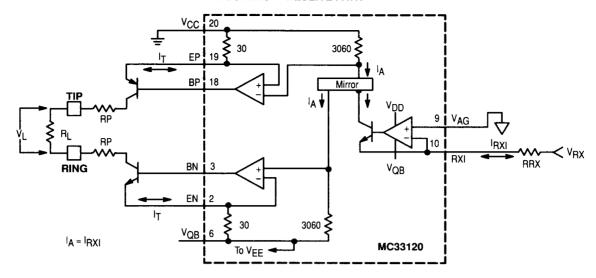

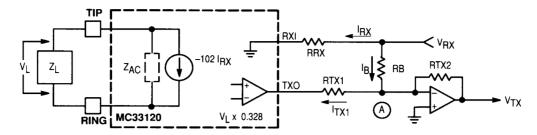

## **Receive Path**

The receive path, shown in Figure 29, consists of the input at RXI, the transistor driver amplifiers, the external transistors, and the load at Tip/Ring.

RXI is a virtual ground (DC level = VAG) and is a current input. Current flow is out of the pin. The RXI current is mirrored to the two transistor drivers which provide a gain of 102. The two external transistors are then two current sources, in series, operating at the same value. An additional internal circuit (not shown) balances the two current sources to maintain operation in their linear region.

The load current (through RI) is slightly different from the transistor current due to the sense resistors RC and RS. The sense resistors add to the DC loop current, but subtract from the AC load current.

In normal operation, the current at RXI is composed of a DC current (from RFO), an AC current (from VRX) which is the receive signal, and an AC current from TXO, which is the feedback signal to set the return loss (setting the return loss is discussed in the section on AC Terminating Impedance). The resulting AC signal at Tip is inverted from that at VRX, while the signal at Ring is in phase with VRX.

The resistors RP are for transient protection, and their value (defined in another section) depends on the amount of protection required. A nominal value of 100  $\Omega$  is suitable for most applications.

The system receive gain, from VRX to Tip/Ring, is not described in this section since in normal applications, it involves the feedback which sets the AC terminating impedance. The Applications Section discusses these in detail.

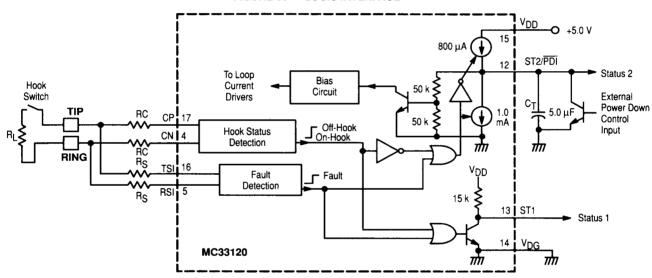

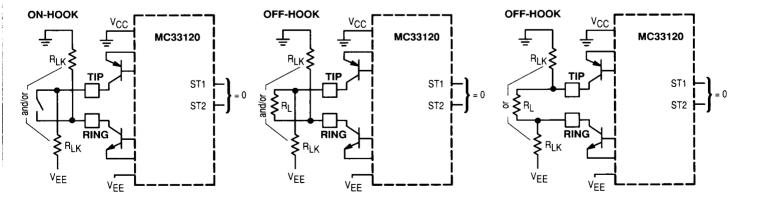

#### Logic Interface (Hook status, pulse dialing, faults)

The logic interface section provides hookswitch status, fault information, and pulse dialing information to the 4-wire side of the system at the ST1 and ST2 outputs. Figure 30 is a representative diagram.

#### FIGURE 29 — RECEIVE PATH

FIGURE 30 — LOGIC INTERFACE

The logic outputs operate according to the truth table in Table 1:

TABLE 1 — STATUS OUTPUT TRUTH TABLE

| Hook     | Fault     | Out | puts |                         |

|----------|-----------|-----|------|-------------------------|

| Status   | Detection | ST1 | ST2  | Circuit Condition       |

| On Hook  | No Fault  | Hi  | Lo   | Internally powered down |

| Off Hook | No Fault  | Lo  | Hi   | Powered up              |

| On Hook  | Fault     | Lo  | Lo   | Internally powered down |

| Off Hook | Fault     | Lo  | Lo   | Internally powered down |

Referring to Figure 30, ST1 is configured as an active NPN pulldown with a 15  $k\Omega$  pullup resistor. ST2 has a 800  $\mu A$  current source pullup, and a 1.0 mA current source for a pulldown. Current limiting this output controls the discharge from the external capacitor when ST2 switches low.

The condition where both ST1 and ST2 are high is not valid, but may occur momentarily during an off-hook to

on-hook transition. The condition where both ST1 and ST2 are low may occur momentarily during an on-hook to off-hook transition — this should not be interpreted as a fault condition. ST1 and ST2 are TTL/CMOS compatible and are powered by the +5.0 V supply ( $V_{DD}$ ). Refer to the Applications Section for more details.

## **Power Supplies, Grounds**

The MC33120 requires 2 power supplies: battery voltage between -42 V and -58 V (V<sub>EE</sub>), and an auxiliary voltage between +4.5 V and +5.5 V (V<sub>DD</sub>).

$V_{EE}$  is nominally -48 V, with a typical range of -42 V to -58 V, and must be referenced to  $V_{CC}$  (battery ground). A 0.1 μF bypass capacitor should be provided between  $V_{CC}$  and  $V_{EE}$ . The  $V_{EE}$  current ( $I_{EE}$ ) is nominally 1.2 mA when on-hook, 10 to 14 mA more than the loop current when off-hook, and  $\approx$ 8.0 mA when off-hook but powered down by using the PDI pin. Ripple and noise rejection from  $V_{EE}$  is a minimum of 40 dB (with a 10 μF capacitor at  $V_{OR}$ ), and

is dependent on the size and quality of the  $V_{QB}$  capacitor ( $C_{QB}$ ) since  $V_{QB}$  is the actual internal supply voltage for the speech amplifiers. The absolute maximum for  $V_{EE}$  is - 60 V, and should not be exceeded by the combination of the battery voltage, its tolerance, and its ripple.

$V_{DD}$  is normally supplied from the line card's digital +5.0 V supply, and is referenced to  $V_{DG}$  (digital ground). A 0.1  $\mu$ F capacitor should be provided between  $V_{DD}$  and  $V_{DG}$ . The  $V_{DD}$  current ( $I_{DD}$ ) is nominally 1.7 mA when on-hook and between 6.0 and 11 mA when off-hook (see Figure 10). When the MC33120 is intentionally powered down using the PDI pin,  $I_{DD}$  changes by <1.0 mA from the normal off-hook value.

$V_{AG}$  is the analog ground for the MC33120, and is the reference for the speech signals (RXI and TXO). Current flow is **into** the pin, and is typically <0.5  $\mu$ A.

Normally, V<sub>CC</sub>, V<sub>DG</sub> and V<sub>AG</sub> are to be at the same DC

level. However, if strong transients are expected at Tip and Ring, as in a Central Office application,  $V_{CC}$  should not be connected directly to  $V_{DG}$  and  $V_{AG}$  in order to prevent possible damage to the +5.0 V system. The MC33120 is designed to tolerate as much as  $\pm 30$  V between  $V_{CC}$  and the other two grounds on a transient basis only. This feature permits  $V_{CC}$  and the other grounds to be kept separate (on an AC basis) on the line card by transient suppressors, or to be connected together farther into the system (at the power supplies). See the Applications Section on ground arrangements and transient protection for further information on connecting the MC33120 to the system supplies.

For operation of the MC33120 at supply voltages other than -42 to -58 V (such as -24 V or -28 V), contact your local Motorola sales office.

#### **APPLICATIONS INFORMATION**

| This section contains information on the following topics:                                                                                                               |                                                                                                          |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|

| Design Procedure       pg. 15         Power Dissipation Calculations       pg. 22         and Considerations       pg. 22         Selecting the Transistors       pg. 23 | Longitudinal Current Capability pg PC Board Layout Considerations pg Alternate Circuit Configurations pg | . 24 |

#### **Design Procedure**

This section describes the step-by-step sequence for designing in the MC33120 SLIC into a typical line card application for either a PBX or Central Office. The sequence is important so that each new component value which is calculated does not affect components previously determined. Figure 4 (Typical Application Circuit) is the reference circuit for most of this discussion. The recommended sequence (detailed below), consists of establishing the DC aspects first, and then the AC aspects:

- Determine the maximum loop current for the shortest line, select RRF. Power dissipation must be considered here.

- Select the main protection resistors (RP), and diodes, based on the expected transient voltages. Transient protection configuration must also be considered here.

- 3) Select RC based on the expected transient voltages.

- Select RS based on the desired longitudinal impedance at Tip and Ring. Transient voltages are also a factor here.

- Calculate RRO based on the desired AC terminating impedance (return loss).

- 6) Calculate RRX based on the desired receive gain.

- Calculate RTX2 and RTX1 based on the desired transmit gain.

- 8) Calculate the balance resistor (RB), or network, as appropriate for desired transhybrid rejection.

- 9) Logic Interface

## Preliminary

There is a primary AC feedback loop which has its main sense points at CP and CN (see Figure 34). The loop extends from there to TXO, through RRO to RXI, through the internal amplifiers to the transistor drivers, through RP to Tip and Ring, and through the RCs to CP and CN. Components within this loop, such as RP, RC, the transistors, and the compensation capacitors need not be tightly matched to each other in order to maintain good longitudinal balance. The tolerance

requirements on these components, and others, are described in subsequent sections. Any components, however, which are placed **outside** the loop for additional line card functions, such as test relay contacts, fuses, resistors in series with Tip and Ring, etc. will affect longitudinal balance, signal balance, and gains if their values and mismatch is not carefully considered. The MC33120 cannot compensate for mismatch among components outside the loop.

The compensation capacitors (0.01  $\mu F$ ) shown at the transistor collectors (Figure 4) compensate the transistor driver amplifiers, providing the required loop stability. The required tolerance on these capacitors can be determined from the following guidelines:

A 10% mismatch ( $\pm$ 5% tolerance) will degrade the longitudinal balance by  $\approx$ 1.0 dB on a 60 dB device, and by  $\approx$ 3.0 dB on a 70 dB device.

A 20% mismatch ( $\pm 10\%$  tolerance) will degrade the longitudinal balance by  $\approx 3.0$  dB on a 60 dB device, and by  $\approx 6.0$  dB on a 70 dB device.

High quality ceramic capacitors are recommended since they serve the secondary function of providing a bleedoff path for RF signals picked up on the phone line. These capacitors should be connected to a good quality RF ground.

The capacitors used at  $C_{QB}$  and  $C_{F}$  must be low leakage to obtain proper performance. Leakage at the  $C_{QB}$  capacitor will affect the DC loop current characteristics, while leakage at the  $C_{F}$  capacitor will affect the AC gain parameters.

1) Maximum Loop Current and Battery Feed Resistance

The maximum loop current (at  $R_L=0$ ) is determined by the RRF resistor between RFO and RXI. The current limit is accomplished by three internal series diodes (see Figure 27) which clamp the voltage across RRF as the loop resistance decreases, thereby limiting the current at RXI. Since the loop current is  $102 \times I_{RXI}$ , the loop current is therefore

clamped. The graphs of Figures 5–7 indicate the maximum loop current at an ambient temperature of +25°C, and after the IC has reached thermal equilibrium (approx. 10 minutes).

Although the maximum loop current is primarily a function of the RRF resistor, it is also affected by ambient temperature, and slightly by VEE. The ambient temperature effects are due to the temperature dependence of the diodes' forward voltage drop, causing the maximum loop current to change by  $\approx -0.3\%/^{\circ}C$ . Changing VEE affects the maximum current in that the power dissipation is changed, thereby changing the die temperature, which affects the diodes' voltage.

The maximum loop current is affected slightly (<5%) by the choice of the RS and RC resistors, since the sense currents through those resistors add to the current supplied by the transistors.

The battery feed resistance is determined by RRF, and is not adjustable independently of the current limit. Defined as  $\Delta V_{TIP}/\Delta I_{L}$ , it is  $\approx\!400~\Omega$ , and is a valid parameter only on long lines where the current limit is not in effect. On short lines, the feed resistance is high since the loop current is clamped at a near constant level. The AC impedance (return loss) however, is not determined nor affected by these DC parameters. Return loss is discussed in another section.

If the application requires that the current limit value have a low temperature dependence, refer to the section following this design sequence which describes an alternate configuration.

#### 2) Main Protection Resistors (RP) and Transient Currents

The purpose of the protection resistors (RP), along with the 4 clamp diodes shown in Figure 4, is to absorb the bulk of the transient energy when transient voltages come in from the phone line. The resistor value must be selected to limit the transient current to a value which can be tolerated by the diodes, while dissipating the energy. The recommended value shown (100  $\Omega$ ) will limit the current from a 1500 V transient to 15 A, which can be carried by 1N4002 diodes under surge conditions. The resistors must be of a type which can tolerate the high instantaneous energy associated with transients. Resistor manufacturers should be consulted for this information.

Referring to Figure 4, a positive transient on either Tip or Ring, or both, will cause the transient current to be delivered to Ground. A negative transient will cause the transient current to come from the VEE supply line. Therefore, the PC board track supplying V<sub>CC</sub> and V<sub>EE</sub> to the MC33120 must be designed to carry the transient currents as well as the normal operating currents. Additionally, since a negative transient will cause a current flow out of the power supply's negative output, which is opposite to the normal flow of current, provisions must be made for this reverse current flow. One suggested method is to place a zener transient suppressor (1N6290A) across the battery supply pins (V<sub>CC</sub> to VFF) physically adjacent to the MC33120. The inductance associated with PC board tracks and wiring will result in insufficient protection for the MC33120 if the suppressor is located at the opposite end of the line card, or at the power

Transient currents can be reduced by increasing the value of RP, with an upper limit determined by the DC conditions on the longest line (highest loop resistance) and minimum VEE supply voltage. These conditions determine the

minimum DC voltage across the transistors, which must be sufficient to handle the largest AC (transmit and receive) signals. If too large a value is selected for RP, the AC signals will be clipped. It is recommended that each transistor have no less than one volt (DC) across their collector to emitter. System AC specifications may require more than this.

Since the RP resistors are within the loop, their tolerance can be  $\pm 5\%$  with no substantial degradation of longitudinal balance. A  $\pm 10\%$  tolerance (20% mismatch) will degrade balance by  $\approx 4.0$  dB on a 65 dB device.

#### FIGURE 32 — RC PROTECTION RESISTORS

#### 3) Selecting the RC Resistors

The primary purpose of the RC resistors is to protect the CP and CN pins from transient voltages and destructive currents. Internally, these pins have clamp diodes to  $V_{CC}$  and  $V_{EE}$  rated for a maximum of 1.0 A under surge conditions only (Figure 32). The 1.0 k $\Omega$  resistors shown in the figures, for example, will provide protection against surges up to 1.0 kV. Resistor manufacturers must be consulted for the proper type of resistor for this environment.

The RC resistors are in series with internal 31 k $\Omega$  resistors, and therefore form a voltage divider to the inputs of the transmit amplifier, as shown in Figure 32. This will affect the transmit gain, receive gain, return loss, and transhybrid rejection (described in subsequent sections). The tolerance of the RC resistors depends on the value selected for them, since any mismatch between them will create a differential voltage at CP and CN when longitudinal voltages are present on Tip and Ring. To ensure a minimum of 58 dB of longitudinal balance, the resistors' absolute value must not differ by more than 39  $\Omega$ . With a nominal value of 1.0 k $\Omega$ , their tolerance must be  $\pm 2\%$ , or less. If their nominal value is 390  $\Omega$  or less, their tolerance can be  $\pm 5\%$ .

#### Longitudinal Impedance (Z<sub>LONG</sub>) — Selecting the RS Resistors

The longitudinal impedance is determined by the RS resistors at the TSI and RSI pins according to the following equation:

$$Z_{LONG} = \frac{RS + 100}{51}$$

(Equation 4)

$Z_{LONG}$  is defined as  $V_{LONG}/I_{LONG}$  as shown in Figure 33; for RS = 9.1 k $\Omega$ ,  $Z_{LONG}$  = 180  $\Omega$ . The calculated value of  $Z_{LONG}$  includes the fact that the RS resistors are in parallel with the synthesized impedance. The tolerance of the RS resistors therefore depends on how much mismatch can be tolerated between the longitudinal impedances at Tip and at Ring. Calculations indicate the two RS resistors

can have a  $\pm 5\%$  tolerance, and still comfortably provide a minimum of 58 dB longitudinal balance.

The resistors must be able to withstand transient voltages expected at Tip and Ring. The TSI and RSI pins have internal

clamp diodes rated for a maximum of 1.0 A under surge conditions only (Figure 33). Resistor manufacturers must be consulted for the proper type of resistor for this environment.

#### FIGURE 33 — LONGITUDINAL IMPEDANCE

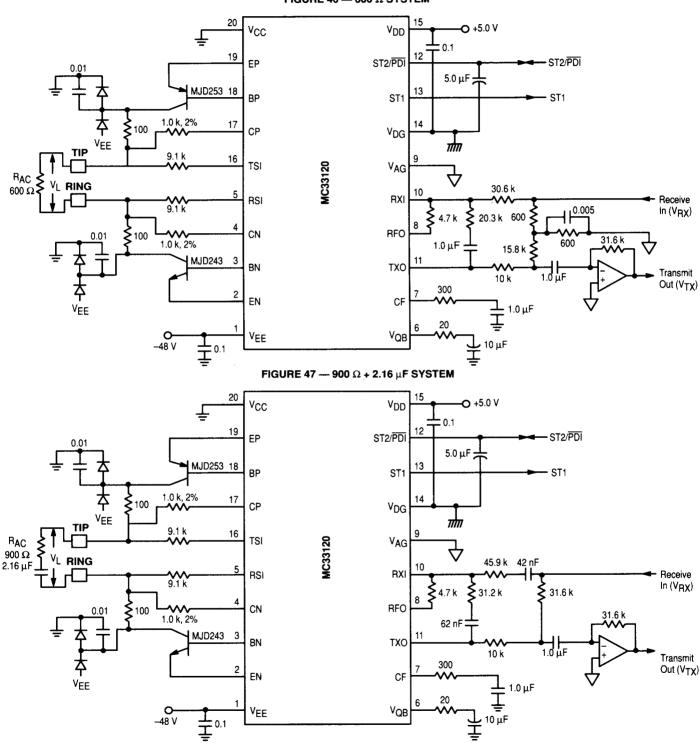

# AC Terminating Impedance and Source Impedance (Z<sub>aC</sub>) — Return Loss

The return loss measurement is a measure of how closely the AC impedance of the SLIC circuit matches the characteristic impedance of the phone line, or a reference impedance. The reference impedance can be, in some cases, a pure resistance (commonly 600  $\Omega$  or 900  $\Omega$ ), a series resistor and capacitor (900  $\Omega$  + 2.16  $\mu$ F), or a more complex network.

To achieve proper return loss with the MC33120, the RRO impedance shown in Figure 34 is to have the same configuration as the reference impedance, but with values scaled according to the equations mentioned below.

CRO, used primarily for DC blocking, is generally a large value (1.0  $\mu$ F) so as to not affect the impedance of RRO. However, it can be included in the RRO network if a complex network is required.

FIGURE 34 — AC TERMINATING IMPEDANCE

$Z_{aC}$  is the impedance looking into the circuit from Tip and Ring (set by RRO), and is defined as  $V_L/I_L$ . Half of  $Z_{aC}$  is from Tip to  $V_{CC}$ , and the other half is from Ring to  $V_{QB}$  (an AC ground). Each half is made up of a synthesized impedance ( $Z_T/2$ ) in parallel with  $R_S$  and (RC + 31 k).

Therefore Zac is equal to:

$$Z_{ac} = [Z_T/2 //R_S//(RC + 31 k)] \cdot 2$$

(Equation 5)

and

$$\frac{Z_T}{2} = \frac{\{R_S//(RC + 31 \text{ k})\} \bullet (Z_{aC}/2)}{\{R_S//(RC + 31 \text{ k})\} - (Z_{aC}/2)}$$

(Equation 6)

The synthesized impedance Z<sub>T</sub> is created as follows:

An incoming signal  $V_L$  produces a differential voltage at CP and CN, and therefore at TXO equal to:

$$V_{TXO} = \frac{V_L \bullet 31 \text{ k} \bullet 0.328}{(\text{RC} + 31 \text{ k})}$$

(Equation 7)

The signal at TXO creates an AC current  $I_{RXI}$  through RRO. RXI is a virtual ground, and CRO is insignificant for first order calculations.

$I_{RXI}$  is gained up by a factor of 102 to produce the current  $I_{T}$  through the transistors.

$Z_T$  is therefore  $V_L/I_T$ . The relationship between  $Z_T$  and RRO is:

$$RRO = \frac{Z_T \cdot 1.037 \cdot 10^6}{(31 \text{ k} + RC)}$$

(Equation 8)

While equation 8 gives the exact value for RRO, a first order approximation is  $Z_{ac}$  • 33.5.

a) Resistive Loads (with RC = 1.0 k, R<sub>S</sub> = 9.1 k): For a 600  $\Omega$  resistive system, Z<sub>T</sub> calculates to 626  $\Omega$ , and RRO calculates to 20.3 k $\Omega$ .

For a 900  $\Omega$  resistive system, ZT calculates to 961  $\Omega,$  and RRO calculates to 31.14 k $\Omega.$

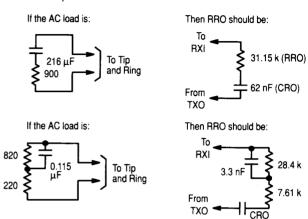

#### b) Complex Loads

For complex (non-resistive) loads, the MC33120 must be made to look like a termination impedance equal to that complex load. This is accomplished by configuring RRO the

same as the complex load, but with all impedance values increased according to the scaling factor of Equation 9.

SF =

$$\frac{[(RC + 31 \text{ k})//RS] \cdot 1.037 \cdot 10^{6}}{(RC + 31 \text{ k}) \cdot [(RC + 31 \text{ k})//R_{S} - (Z_{aC}/2)]} \text{ (Equation 9)}$$

Z<sub>ac</sub> is computed at a nominal frequency of interest. A first order approximation of Equation 9 is:

$$SF = 1.037 \cdot 10^6 / (RC + 31 \text{ k})$$

(Equation 9a)

For example:

CRO must remain in series with the network to provide DC blocking. If the load network does not include a series capacitor (as in the second example above), CRO should be large (1.0  $\mu F)$  so its impedance does not affect the RRO network. The above procedure will yield a return loss measurement which is constant with respect to frequency. The RRO resistor, or network, must have a tolerance equal to or better than the required system tolerance for return loss and receive gain.

## 6) Receive Gain (GRX)

The receive gain involves the same circuit as Figure 34, but with the addition of the RRX resistor (or network) which sets the receive gain. See Figure 35.

#### FIGURE 35 — RECEIVE GAIN

The receive gain (GRX), defined as the voltage gain from V<sub>RX</sub> to V<sub>I</sub>, is calculated as follows:

RXI is a virtual ground, and Rac is the AC impedance of the load (phone line).

The AC current generated in the transistors is 102 • IRXI. which is equal to 102 • (I<sub>R</sub> − I<sub>TXO</sub>).

$I_R = V_{RX}/RRX$ , and

$$I_{TXO} = \frac{V_{TXO}}{RRO} = \frac{V_L \cdot 31 \text{ k} \cdot 0.328}{RRO \cdot (31 \text{ k} + RC)}$$

(Equation 10)

Using equations 5 and 8, involving Zac, RS and RC, and the above equations yields:

$$\frac{V_L}{V_{RX}} = G_{RX} = \frac{102 \cdot (R_{ac} / / Z_{ac})}{RRX}$$

(Equation 11)

Therefore, RRX =

$$\frac{102 \bullet (R_{ac}//Z_{ac})}{G_{RX}}$$

(Equation 12)

Equation 12 applies only for the case where Rac and Zac have the same configuration. If they also have the same magnitude, then set RRX = 51 • Rac to set a receive gain of 0 dB. The AC source impedance of the above circuit to Tip and Ring is  $Z_{ac}$ . For the case where  $R_{ac} \neq Z_{ac}$ , use the following equation:

$$\frac{V_L}{V_{RX}} = \frac{102}{RRX \cdot \left[\frac{1}{Z_L} + \frac{1.037 \cdot 10^6}{(31k + RC) \cdot RRO}\right]}$$

(Equation 13)

where

$$Z_L = \left[ \frac{R_{ac}}{2} // RS // (RC + 31 k) \right] \cdot 2$$

(Equation 14)

#### a) Resistive Loads

For a 600  $\Omega$  resistive system, set RRX = 30.6 k $\Omega$ , and for a 900  $\Omega$  resistive system, set RRX = 45.9 k $\Omega$ .

#### b) Complex Loads

For complex (non-resistive) loads, the RRX resistor needs to be replaced with a network having the same configuration as the complex load, but with all impedance values scaled up by a factor of 51 (for 0 dB gain). If a gain other than 0 dB is desired, the scaling factor is determined from Equation 12. This methods applies only if the RRO network has been made complex comparable to the load according to the procedure in the previous section (Equations 5-9a), such that Rac = Zac. Using a scaling factor of 51, and the previous examples, yields:

If the AC load is: Then RRX should be: 2.16 µF To Tip RXI 45.9 k 42 nF If the AC load is: Then RRX should be:

The preceeding procedure will yield a receive gain which is constant with respect to frequency. The RRX resistor, or network, must have a tolerance equal to or better than the required system tolerance for receive gain.

### 7) Transmit Gain (GTX)

Setting the transmit gain involves selecting RTX1 and RTX2 in Figure 28. The voltage gain from V<sub>I</sub> to V<sub>TX</sub> is calculated from the following:

$$G_{TX} = \frac{V_{TX}}{V_I} = \frac{RTX2 \cdot 31 \text{ k} \cdot 0.328}{RTX1 \cdot (RC + 31 \text{ k})}$$

(Equation 15)

For 0 dB gain, set RTX2 =  $3.15 \times RTX1$  (for RC =  $1.0 \times k$ ). The actual values of RTX2 and RTX1 are not critical — only their ratio so as to provide the proper gain at the op amp. Once the ratio is established, the two resistors can be selected from a set of standard resistor values. The minimum value for RTX1 is limited by the drive capability of TXO, which is a nominal ±800 μA peak (±275 μA minimum). As a general rule, RTX1 should be between 6.0 k $\Omega$  and 20 k $\Omega$ . The load on TXO is the parallel combination of RTX1 and RRO.

CTX is for DC blocking, and is typically a large value (1.0 µF) so as to not be a significant impedance. In general, it should not be used for low frequency rolloff as that will affect the transhybrid rejection (discussed in the next section). Low frequency rolloff should be done after the op amp. High frequency rolloff can be set by placing a capacitor across RTX2.

For complex loads (at Tip and Ring), if RRO and RRX have been made complex comparable to the load as described in the previous sections, neither RTX1 nor RTX2 needs to be complex since both the transmit and receive signals which appear at TXO will be flat with respect to frequency.

RTX1 and RTX2 must have a tolerance equal to or better than the required system tolerance for the transmit gain.

#### 8) Balance Network (RB) — Transhybrid Rejection

When a receive signal is applied to V<sub>BX</sub> to produce a signal at Tip and Ring, the two-to-four wire arrangement of a hybrid (the MC33120) results in a reflected signal at TXO. Transhybrid rejection involves canceling that reflected signal before it appears at V<sub>TX</sub>. The method used is to insert the RB resistor (or network) as shown in Figure 36. The current IB, supplied form VRX, cancels the current ITX1 supplied from TXO (Node A is a virtual ground). Good transhybrid cancellation requires that the currents be equal in magnitude and 180° out of phase at node A.

Using the equations for transmit and receive gains, the current ITX1 is equal to:

$$I_{TX1} = \frac{33.5 \bullet V_{RX} \bullet Z_{ac} \bullet Z_{L} \bullet 31 \text{ k}}{RRX \bullet [Z_{ac} + Z_{L}] \bullet RTX1 \bullet (RC + 31 \text{ k})}$$

(Equation 16)

a) For the case where RRO and RRX are comparable in configuration to ZL:

Since  $I_B = V_{BX}/RB$ , then RB can be determined from:

$$RB = \frac{RRX \bullet RTX1 \bullet (RC + 31 \text{ k})}{33.5 \bullet [Z_{aC}//Z_1] \bullet 31 \text{ k}}$$

(Equation 17)

#### FIGURE 36 --- BALANCE RESISTOR

Equation 17 provides a value for an RB resistor which will provide the correct magnitude for  $I_B.$  The correct phase relationship is provided by the fact that the signal at TXO is out of phase with that at  $V_{RX}.$  The phase relationship will be  $180^{\circ}$  only if RRO and RRX are of a configuration identical to that of the load. This applies regardless of whether the load,  $Z_L,$  (and RRO and RRX) are purely resistive or of a complex nature. Equation 17 reduces to a non-complex resistance if RRX,  $Z_{aC},$  and  $Z_L$  are all comparably complex.

For the case where  $Z_{ac} = Z_L$ , RRX = 51 •  $Z_{ac}$ , and RC = 1.0 k, Equation 17 reduces to:

b) For the case where  $Z_{ac}$  and  $Z_L$  do not have the same frequency characteristics:

For the case where, for reasons of cost and/or simplicity, the load (R<sub>I</sub>) is considered resistive (whereas in reality it is not a pure resistance) and therefore resistors, rather than networks, were selected for RRO and RRX, using a simple resistor for RB may not provide sufficient transhybrid rejection due to a phase angle difference between VRX and TXO. The terminating impedance may therefore not necessarily be matched exactly to the line impedance, but the resulting circuit still provides sufficiently correct performance for receive gain, transmit gain, and return loss. The rejection can be improved in this case by replacing RB with the configuration shown in Figure 37. Even on a very short phone line there is a reactive component to the load due to the two compensation capacitors (CC, Figure 4) at the transistor collectors. The two capacitors can be considered in series with each other, and across the load as shown in Figure 37. To simplify the explanation, the current source and Zac of Figure 36 are replaced with the Thevenin voltage source and series Zac. Since ZL and Zac are not matched, there will

be a phase shift from  $V_{RX}$  to the signal across Tip and Ring. This phase shift is also present at TXO. The same phase shift is generated at node B in the RB network by making RB1 equal to  $Z_{ac}$ , and  $Z_L$  equal to the load. RB2 is then calculated from:

$$RB2 = \frac{RRX \cdot RTX1 \cdot (RC + 31 \text{ k})}{33.5 \cdot Z_{AC} \cdot 31 \text{ k}}$$

(Equation 19)

For example, for a system where the load is considered a 600  $\Omega$  resistor (RRO = 20.3 k $\Omega$ , RRX = 30.6 k $\Omega$ , RTX1 = 10 k $\Omega$ , and RC = 1.0 k $\Omega$ ), RB1 would be a 600  $\Omega$  resistor, Z<sub>L</sub> (in the RB network) would be a 600  $\Omega$  resistor in parallel with a 0.005  $\mu$ F capacitor, and RB2 calculates to 15.715 k $\Omega$ .

The RB resistor, or network, must have a tolerance equal to or better than the required system tolerance for transhybrid rejection.

#### 9) Logic Interface

The logic circuit (output ST1, and the I/O labeled ST2/PDI) is depicted in Figure 30, and functions according to the truth table in Table 1.

#### a) Output Characteristics

ST1 is a traditional NPN pull-down with a 15 k $\Omega$  pull-up resistor. Figures 19 and 20 indicate its output characteristics.

ST2 is configured with the following items: a) a 1.0 mA current source for a pull-down which is active only when ST2 is internally set low; b) an 800  $\mu$ A current source pull-up which is active only when ST2 is internally set high; c) a positive feedback aspect within this output circuit which provides considerable hysteresis for stability reasons. Its output characteristics are shown in Figures 21 and 22. Due to this configuration, any external pull-up resistance which is applied to this pin must be greater than 15 k $\Omega$ , or the output may not reliably switch from high to low. Any external pull-down resistance does not affect this output's ability to

FIGURE 37 — BALANCE NETWORK

switch from low-to-high, but does affect the maximum longitudinal currents which can be accepted by the circuit (see the section on Longitudinal Current capability). The capacitor (C<sub>T</sub>) is required to provide a time delay, for stability reasons, during transitions between off-hook and on-hook. This capacitor additionally affects maximum longitudinal currents, as well as stability during pulse dialing (explained below).

#### b) Hook Status

The MC33120 uses the sense currents at CP and CN to activate the hook status circuit. The sensing is configured such that the circuit monitors the impedance across Tip/Ring, which results in the hookswitch thresholds being virtually independent of the battery voltage. The off-hook to on-hook threshold is affected by the choice of RRF according to the graph of Figure 8, but is not affected by the value of RS. The on-hook to off-hook threshold is affected by the value of RS according to the graph of Figure 9, but is not affected by RRF. Varying the RC resistors does not affect the thresholds significantly.

When the telephone is on-hook (ST1 = Hi, ST2 = Low), the MC33120 is internally powered down, the external transistors are shut off, and power consumption is at a minimum. Upon closure of the phone's hookswitch, ST1 will switch low within 10 us. ST2 will then change state slowly due to the external capacitor ( $C_T = 5.0 \mu F$ ). There is a  $\approx 8.0 \text{ millisecond}$ delay for ST2 to reach the threshold necessary to activate the internal bias circuit, which in turn activates the external drive transistors to supply loop current. This delay is necessary to prevent instabilities during the transition to off-hook.

Upon opening the telephone's hookswitch, ST1 will switch high within ≈200 μs. ST2 then requires ≈60 ms to reach the threshold to switch off the internal bias circuit, which in turn shuts down the external drive transistors.

#### c) Pulse Dialing

During pulse dialing, ST1 will change state concurrent with the hookswitch. ST2 is kept from switching during pulse dialing by the external capacitor (CT), which keeps the MC33120 in a powered up condition and stable. If the CT capacitor is too small, the voltage at ST2 could droop to the PDI threshold (see section e below) during each pulse. This could cause the MC33120 to create additional noise on the

line as it would cycle between a power-up and power-down condition with each dialing pulse.

#### d) Fault Detection

Faults are defined as excessive leakage from Tip to VFF and/or ground, and from Ring to VEE and/or ground. A single fault is any one of the above conditions, while a double fault is defined as excessive leakage from Tip to VFF and from Ring to V<sub>CC</sub>, as depicted in Figure 38. Refer to Figures 11–15 for the resistance, RLK, which will cause the MC33120 to switch to a power-down condition. If the leakage resistance is less than that indicated in the graphs, the MC33120 will power-down itself and the two external transistors, thereby protecting them from overheating. Both status outputs (ST1 and ST2) will be at a logic low, indicating a fault condition. A fault condition is detected by monitoring an imbalance in the magnitudes of the currents at TSI and RSI, and/or a polarity reversal at Tip and Ring.

The MC33120 will detect the following conditions:

#### 1) When on-hook (see Figure 11):

- a)  $<2.0 \text{ k}\Omega$  between Ring and  $V_{CC}$ , with no hysteresis at this threshold, or

- b) <2.5 k $\Omega$  between Tip and V<sub>EE</sub>, with no hysteresis at this threshold, or

- c) Both a and b simultaneously.

Leakage from Tip to VCC and/or Ring to VEE are not detected as faults while the MC33120 is on-hook.

#### 2) When off-hook (600 $\Omega$ between Tip and Ring):

- a) <500  $\Omega$  between Tip and V<sub>CC</sub>, or

- b) <600  $\Omega$  between Tip and V<sub>EE</sub>, or

- c) <500  $\Omega$  between Ring and  $\overline{V}_{EE}$ , or

- d) <600  $\Omega$  between Ring and V<sub>CC</sub>, or

- e) Both b and d simultaneously

A simultaneous occurrence of conditions a) and c) is not detected as a fault. See Figures 12-15 for the threshold variation with R<sub>L</sub>. Resetting of the fault detection circuit requires that the leakage resistance be increased to a value between 10 k $\Omega$  and 20 k $\Omega$ , depending on V<sub>EE</sub>, R<sub>L</sub>, and R<sub>S</sub>. Both ST1 and ST2 should be monitored for hookswitch status to preclude not detecting a fault condition.

Figure 15 indicates the variation in fault thresholds for Tip-to-V<sub>CC</sub> and Ring-to-Battery faults, and is valid only for loop resistances of 200  $\Omega$  to 1.0 k $\Omega$ . On loops larger than

#### FIGURE 38 — FAULT DETECTION

MC33120 MOTOROLA 1.0 k $\Omega$ , the MC33120 does not reliably indicate the fault condition at ST1 and ST2, but may indicate on-hook status instead. This does not apply to Tip-to-Battery and Ring-to-V<sub>CC</sub> faults which are correctly detected for lines beyond 1.0 k $\Omega$ .

#### e) PD! Input

The ST2 output can also be used as an input (PDI input) to power down the circuit, denying loop current to the subscriber (by shutting off the external pass transistors), regardless of the hookswitch position. Powering down is accomplished by pulling PDI to a logic low with an open collector output, or an NPN transistor as shown in Figure 30. The switching threshold is  $\approx+1.5$  V. The current out of PDI, when pulled low, is  $\approx800~\mu$ A. Releasing PDI allows the MC33120 to resume normal operation.

If the external telephone is off-hook while the MC33120 is powered down, sense currents at CP and TSI will result in some loop current flowing through the loop and back into CN and RSI. This current is generally on the order of 1.0 to 3.0 mA, determined primarily by the RS resistors, loop resistance, and  $V_{EE}$ . ST1 will continue to indicate the telephone's actual hook status while PDI is held low. The on-to-off hook threshold is the same as that during normal operation, but the off-to-on hook threshold is >250 k $\Omega$ .

When powered down with the PDI pin, the receive gain (V<sub>RXI</sub> to Tip/Ring) is muted by >90 dB, and the transmit gain (Tip/Ring to TXO) is muted by >30 dB.

## Power Dissipation, Calculation and Considerations

#### a) Reliability

The maximum power dissipated by the MC33120 must be considered, and managed, so as to not exceed the junction temperature listed in the Absolute Maximum Ratings. Exceeding this temperature on a recurring basis will reduce long term reliability, and possibly degrade performance. The junction temperature also affects the statistical lifetime of the device, due to long term thermal effects within the package. Today's plastic integrated circuit packages are as reliable as ceramic packages under most environmental conditions. However, when the ultimate in system reliability is required, thermal managements must be considered as a prime system design goal.

Modern plastic package assembly technology utilizes gold wire bonded to aluminum bonding pads throughout the electronics industry. When exposed to high temperatures for protracted periods of time an intermetallic compound can form in the bond area resulting in high impedance contacts and degradation of device performance. Since the formation of intermetallic compounds is directly related to device junction temperature, it is incumbent on the designer to determine that the device junction temperature is consistent with system reliability goals.

Based on the results of almost ten years of +125°C operating life testing, Table 2 has been derived indicating the relationship between junction temperature and time to 0.1% wire bond failure.

**TABLE 2 — STATISTICAL LIFETIME**

| Time<br>(Hours) | Time<br>(Years)                                         |

|-----------------|---------------------------------------------------------|

| 1,032,200       | 117.8                                                   |

| 419,300         | 47.9                                                    |

| 178,700         | 20.4                                                    |

| 79,600          | 9.4                                                     |

| 37,000          | 4.2                                                     |

| 17,800          | 2.0                                                     |

| 8,900           | 1.0                                                     |

|                 | (Hours)  1,032,200 419,300 178,700 79,600 37,000 17,800 |

Motorola MECL Device Data, DL122

The "time" in Table 2 refers to the time the device is operating at that junction temperature. Since the MC33120 is at a low power condition (nominally 68 mW) when on-hook, the duty cycle must be considered. For example, if a statistical duty cycle of 20% off-hook time is used, operation at 130°C junction temperature (when off-hook) would result in a statistical lifetime of ≈10 years.

## b) Power and Junction Temperature Calculation

The power within the IC is calculated by subtracting the power dissipated in the two wire side (the transistors and the load) from the power delivered to the IC by the power supplies. Refer to Figure 4 and 27.

$$P_D = |V_{DD} \cdot I_{DD}| + |V_{EE} \cdot I_{EE}| - (|I_{LOOP} \cdot |V_{EP} - V_{EN}|)$$

(Equation 20)

The terms V<sub>EP</sub> and V<sub>EN</sub> are the DC voltages, with respect to ground, at the EP and EN pins. These voltages can be measured, or can be approximated by:

$$V_{EP} \approx - (30 \ \Omega \bullet I_{LOOP})$$

$V_{EN} \approx V_{EE} + 2.1 \ V + (I_{LOOP} \bullet 35 \ \Omega)$

Refer to Figure 23. The junction temperature is then calculated from:

$$T_J = T_A + (P_D \bullet \theta_{JA})$$

(Equation 21)

where  $T_A$  is the ambient air temperature at the IC package, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance shown in Figure 39. The highest junction temperature will occur at maximum  $V_{EE}$  and  $V_{DD}$ , maximum loop current, and maximum ambient temperature.