# MICROCOMPUTER COMPONENTS

# COUNTER TIMER CIRCUIT MK3882

#### **FEATURES**

- ☐ All inputs and outputs fully TTL compatible

- □ Each channel may be selected to operate in either Counter Mode or Timer Mode

- Used in either mode, a CPU-readable Down Counter indicates number of counts-to-go until zero

- A Time Constant Register can automatically reload the Down Counter at Count Zero in Counter and Timer Mode

- Selectable positive or negative trigger initiates time operation in Timer Mode. The same input is monitored for event counts in Counter Mode.

- ☐ Three channels have Zero Count/Timeout outputs capable of driving Darlington transistors

- □ Interrupts may be programmed to occur on the zero count condition in any channel

- Daisy chain priority interrupt logic included to provide for automatic interrupt vectoring without external logic

#### INTRODUCTION

The Z80-Counter Timer Circuit (CTC) is a programmable component with four independent channels that provide counting and timing functions for microcomputer systems based on the Z80-CPU. The CPU can configure the CTC channels to operate under various modes and conditions as required to interface with a wide range of devices. In most applications, little or no external logic is required. The Z80-CTC utilizes N-channel silicon gate depletion load technology and is packaged in a 28-pin DIP. The Z80-CTC requires only a single 5 volt supply and a one-phase 5 volt clock.

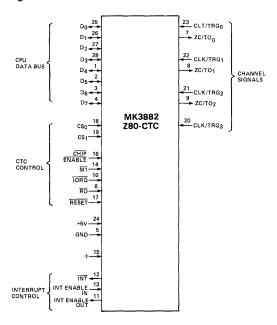

#### CTC PIN DESCRIPTION

A diagram of the Z80-CTC pin configuration is shown in Figure 1. This section describes the function of each pin.

D<sub>7</sub>-D<sub>0</sub>

Z80-CPU Data Bus (bidirectional, tristate)

This bus is used to transfer all data and command words between the Z80-CPU and

## **Z80-CTC PIN CONFIGURATION**

Figure 1

the Z80-CTC. There are 8 bits on this bus, of which  $\mathbf{D}_{\mathbf{0}}$  is the least significant.

CS1-CS0 Channel Select (input, active high)

These pins form a 2-bit binary address code for selecting one of the four independent CTC channels for an I/O Write or Read (See truth table below.)

|     | CS1 | CSO |

|-----|-----|-----|

| Ch0 | 0   | 0   |

| Ch1 | 0   | 1   |

| Ch2 | 1   | 0   |

| Ch3 | 1   | 1   |

Œ

Chip Enable (input, active low)

A low level on this pin enables the CTC to accept control words, Interrupt Vectors, or time constant data words from the Z80 Data

VII

Bus during an I/O Write cycle, or to transmit the contents of the Down Counter to the CPU during an I/O Read cycle. In most applications this signal is decoded from the 8 least significant bits of the address bus for any of the four I/O port addresses that are mapped to the four Counter/Timer Channels.

Clock (Φ) System Clock (input)

> This single-phase clock is used by the CTC to synchronize certain signals internally.

Machine Cycle One Signal from CPU (input, active low)

> When M1 is active and the RD signal is active, the CPU is fetching an instruction from memory. When M1 is active and IORQ is active, the CPU is acknowledging an interrupt, alerting the CTC to place an Interrupt Vector on the Z80 Data Bus if it has daisy chain priority and one of its channels has requested an interrupt.

Input/Output Request from CPU (input, active low)

> The IORO signal is used in conjunction with the CE and RD signals to transfer data and Channel Control Words between the Z80-CPU and the CTC. During a CTC Write Cycle, IORQ and CE must be true and RD false. The CTC does not receive a specific write signal, instead generating its own internally from the inverse of a valid RD signal. In a CTC Read Cycle, IORO, CE and RD must be active to place the contents of the Down Counter on the Z80 Data Bus. If IORQ and M1 are both true, the CPU is acknowledging an interrupt request, and the highest-priority interrupting channel will place its Interrupt Vector on the Z80 Data Bus.

RD Read Cycle Status from the CPU (input, active low)

> The RD signal is used in conjunction with the IORQ and CE signals to transfer data and Channel Control Words between the Z80-CPU and the CTC. During a CTC Write Cycle, IORQ and CE must be true and RD false. The CTC does not receive a specific write signal, instead generating its own internally from the inverse of a valid RD signal. In a CTC Read Cycle, IORQ, CE and RD must be active to place the contents of the Down Counter on the Z80 Data Bus.

Interrupt Enable In (input, active high) This signal is used to help form a systemwide interrupt daisy chain which establishes priorities when more than one peripheral device in the system has interrupting

capability. A high level on this pin indicates that no other interrupting devices of higher priority are being serviced by the Z80-CPU.

Interrupt Enable Out (output, active high) The IEO signal, in conjunction with IEI, is used to form a system-wide interrupt priority daisy chain. IEO is high only if IEI is high and the CPU is not servicing an interrupt from any CTC channel. Thus this signal blocks lower priority devices from interrupting while a higher priority device is being serviced by the CPU.

ĪNĪ Interrupt Request (output, open drain, active low)

> This signal goes true when any CTC channel which has been programmed to enable interrupts has a zero-count condition in its Down Counter.

RESET Reset (input, active low)

> This signal stops all channels from counting and resets channel interrupt enable bits in all control registers, thereby disabling CTCgenerated interrupts. The ZC/TO and INT outputs go to their inactive states, IEO reflects IEI, and the CTC's data bus output drivers go to the high impedance state.

CLK/TRG3-External Clock/Timer Trigger (input, user-CLK/TRG0 selectable active high or low)

> There are four CLK/TRG pins, corresponding to the four independent CTC channels. In the Counter Mode, every active edge on this pin decrements the Down Counter. In the Timer Mode, an active edge on this pin initiates the timing function. The user may select the active edge to be either rising or falling.

ZC/TO2-Zero Count/Timeout (output, active high) ZC/TO0 There are three ZC/TO pins, corresponding to CTC channels 2 through 0. (Due to package pin limitations channel 3 has no ZC/TO pin.) In either Counter Mode or Timer Mode, when the Down Counter decrements to zero an active high going pulse appears at this pin.

For further details on this device, please consult the CTC MK3882 Technical Manual, included in Section IV.

**VII-18**

**IEO**

M<sub>1</sub>

IORQ

ΙEΙ

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias                    | Specified operating range |

|-------------------------------------------|---------------------------|

| Storage Temperature                       | 65°C to +150°C            |

| Voltage On Any Pin With Respect To Ground | 0.3 V to +7 V             |

| Power Dissipation                         | 0.8 W                     |

All ac parameters assume a load capacitance of 100 pF max. Timing references between two output signals assume a load difference of 50 pF max.

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## D.C. CHARACTERISTICS

$T_A$  = 0°C to 70°C,  $V_{CC}$  = 5 V  $\pm$  5% unless otherwise specified

| SYMBOL           | PARAMETER                                 | MIN               | MAX                 | UNIT | TEST CONDITION                     |

|------------------|-------------------------------------------|-------------------|---------------------|------|------------------------------------|

| V <sub>ILC</sub> | Clock Input Low Voltage                   | -0.3              | 0.80                | ٧    |                                    |

| V <sub>IHC</sub> | Clock Input High Voltage (1)              | V <sub>CC</sub> 6 | V <sub>CC</sub> +.3 | ٧    | 1                                  |

| V <sub>IL</sub>  | Input Low Voltage                         | -0.3              | 0.8                 | ٧    |                                    |

| V <sub>IH</sub>  | Input High Voltage                        | 2.0               | V <sub>cc</sub>     | V    | ]                                  |

| V <sub>OL</sub>  | Output Low Voltage                        |                   | 0.4                 | ٧    | I <sub>OL</sub> = 2 mA             |

| V <sub>OH</sub>  | Output High Voltage                       | 2.4               |                     | V    | I <sub>OH</sub> = -250 μA          |

| I <sub>cc</sub>  | Power Supply Current                      |                   | 120                 | mA   | T <sub>C</sub> = 400 nsec**        |

| ال               | Input Leakage Current                     |                   | ±10                 | μΑ   | $V_{IN} = 0$ to $V_{CC}$           |

| I <sub>LOH</sub> | Tri-State Output Leakage Current in Float |                   | 10                  | μΑ   | $V_{OUT} = 2.4 \text{ to } V_{CC}$ |

| I <sub>LOL</sub> | Tri-State Output Leakage Current in Float |                   | -10                 | μΑ   | V <sub>OUT</sub> = 0.4 V           |

| I <sub>OHD</sub> | Darlington Drive Current                  | -1.5              |                     | mA   | V <sub>OH</sub> = 1.5 V            |

\*\*TC = 250 nsec for MK3882-4

## CAPACITANCE

$T_A = 25^{\circ}C$ , f = 1 MHz

| SYMBOL           | PARAMETER          | MAX | UNIT | TEST CONDITION     |

|------------------|--------------------|-----|------|--------------------|

| C <sub>Φ</sub>   | Clock Capacitance  | 20  | pF   | Unmeasured Pins    |

| C <sub>IN</sub>  | Input Capacitance  | 5   | pF   | Returned to Ground |

| C <sub>OUT</sub> | Output Capacitance | 10  | pF   |                    |

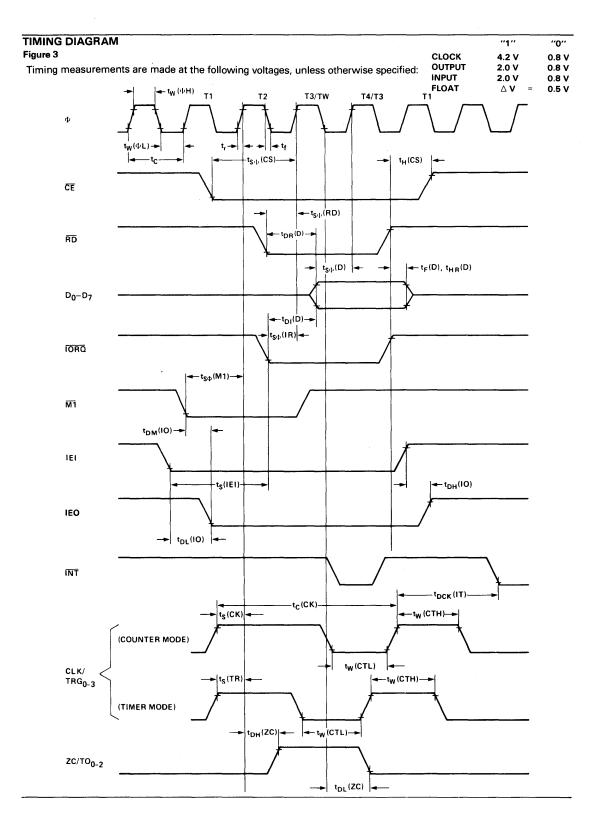

## A.C. CHARACTERISTICS MK3882, MK3882-10, Z80-CTC

$T_A$  = 0°C to 70°C,  $V_{CC}$  = +5 V  $\pm$  5%, unless otherwise noted

|                                 |                                                                   |                                                                                                            | 38823882-4          |                             |                     |                             |          |                                         |

|---------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------|---------------------|-----------------------------|----------|-----------------------------------------|

| SIGNAL                          | SYMBOL                                                            | PARAMETER                                                                                                  | MIN                 | MAX                         | MIN                 | MAX                         | UNIT     | COMMENTS                                |

| Φ                               | $t_{C}$ $t_{W}$ ( $\Phi$ H) $t_{W}$ ( $\Phi$ L) $t_{r}$ , $t_{f}$ | Clock Period<br>Clock Pulse Width, Clock High<br>Clock Pulse Width, Clock Low<br>Clock Rise and Fall Times | 400<br>170<br>170   | (1)<br>2000<br>2000<br>30   | 250<br>105<br>105   | (1)<br>2000<br>2000<br>30   | ns<br>ns |                                         |

|                                 | t <sub>H</sub>                                                    | Any Hold Time for Specified Setup Time                                                                     | 0                   | j                           | 0                   |                             | ns       |                                         |

| CS, CE, etc.                    | t <sub>S</sub> Φ(CS)                                              | Control Signal Setup Time to<br>Rising Edge of ⊕ During Read<br>or Write Cycle                             | 160                 |                             | 145                 |                             | ns       |                                         |

|                                 | t <sub>D</sub> Φ(D)<br>t <sub>S</sub> Φ(D)                        | Data Output Delay from Rising<br>Edge of $\Phi$ During Read Cycle<br>Data Setup Time to Rising Edge        | 60                  | 240                         | 50                  | 200                         | ns<br>ns | (2)                                     |

| D <sub>0</sub> - D <sub>7</sub> | t <sub>Di</sub> (D)                                               | of Ф During Write or M1 Cycle Data Output Delay from Falling Edge of IORQ During INTA Cycle                |                     | 340                         | į:                  | 160                         | ns       | (2)                                     |

|                                 | t <sub>F</sub> (D)                                                | Delay to Floating Bus (Output<br>Buffer Disable Time)                                                      |                     | 230                         | :                   | 110                         | ns       |                                         |

| IEI                             | t <sub>S</sub> (IEI)                                              | IEI Setup Time to Falling Edge of IORQ During INTA Cycle                                                   | 200                 |                             | 140                 |                             | ns       | , , , , , , , , , , , , , , , , , , , , |

|                                 | t <sub>DH</sub> (IO)                                              | IEO Delay Time from Rising Edge of IEI                                                                     |                     | 220                         |                     | 160                         | ns       | (3)                                     |

|                                 | t <sub>DL</sub> (IO)                                              | IEO Delay Time from Falling Edge of IEI                                                                    |                     | 190                         |                     | 130                         | ns       | (3)                                     |

| IEO                             | t <sub>DM</sub> (IO)                                              | IEO Delay from Falling Edge of M1 (Interrupt Occurring just Prior to M1)                                   |                     | 300                         |                     | 190                         | ns       | (3)                                     |

| IORQ                            | t <sub>S</sub> Φ(IR)                                              | IORQ Setup Time to Rising Edge<br>of Φ During Read or Write Cycle                                          | 250                 |                             | 115                 |                             | ns       |                                         |

| M1                              | t <sub>S</sub> Φ(M1)                                              | M1 Setup Time to Rising Edge<br>of ⊕ During INTA or M1 Cycle                                               | 210                 |                             | 90                  |                             | ns       |                                         |

| RD                              | t <sub>S</sub> Φ(RD)                                              | RD Setup Time to Rising Edge of Φ During Read or M1 Cycle                                                  | 240                 |                             | 115                 |                             | ns       |                                         |

| INT                             | t <sub>D</sub> Φ(IT)                                              | $\overline{INT}$ Delay from Rising Edge of $\Phi$                                                          |                     | t <sub>C</sub> (Φ) +<br>200 |                     | t <sub>C</sub> (Φ) +<br>140 |          | (7)                                     |

|                                 | t <sub>C</sub> (CK)<br>t <sub>r</sub> , t <sub>f</sub>            | Clock Period Clock and Trigger Rise and Fall Times                                                         | 2t <sub>C</sub> (Φ) | 50                          | 2t <sub>C</sub> (Φ) | 50                          | ns       | (5)                                     |

|                                 | t <sub>S</sub> (CK)                                               | Clock Setup Time to Rising Edge of $\Phi$ for Immediate Count                                              | 210                 |                             | 130                 |                             | ns       | (5)                                     |

| ·                               | t <sub>S</sub> (TR)                                               | Trigger Setup Time to Rising Edge of $\Phi$ for Enabling of Prescaler on Following Rising Edge of $\Phi$   | 210                 |                             | 130                 |                             | ns       | (6)                                     |

| CLK/<br>TRG <sub>0-3</sub>      | t <sub>W</sub> (CTH)                                              | Clock and Trigger High Pulse Width                                                                         | 200                 |                             | 120                 |                             | ns       | (7)                                     |

|                                 | t <sub>W</sub> (CTL)                                              | Clock and Trigger Low Pulse<br>Width                                                                       | 200                 |                             | 120                 |                             | ns       | (7)                                     |

## A.C. CHARACTERISTICS MK3882, MK3882-10, Z80-CTC (Cont'd)

$\rm T_A$  = 0°C to 70°C,  $\rm V_{CC}$  = +5 V  $\pm$  5%, unless otherwise noted

|                          |                      |                                                          | 3882 |     | 3882-4 |     |      | 1        |

|--------------------------|----------------------|----------------------------------------------------------|------|-----|--------|-----|------|----------|

| SIGNAL                   | SYMBOL               | PARAMETER                                                | MIN  | MAX | MIN    | MAX | UNIT | COMMENTS |

|                          | t <sub>DH</sub> (ZC) | ZC/TO Delay Time from Rising Edge of Φ, ZC/TO High       |      | 190 |        | 120 | ns   | (7)      |

| ZC/<br>TO <sub>0-2</sub> | t <sub>DL</sub> (ZC) | ZC/TO Delay Time from Falling Edge of $\Phi$ , ZC/TO Low |      | 190 |        | 120 | ns   | (7)      |

#### NOTES:

- 1.  $t_C = t_W (\Phi H) + t_W (\Phi L) + t_r + t_f$ .

- Increase delay by 10 nsec for each 50 pF increase in loading 200 pF maximum for data lines and 100 pF for control lines.

- Increase delay by 2 nsec for each 10 pF increase in loading, 100 pF maximum.

- 4. RESET must be active for a minimum of 3 clock cycles.

- 5. Counter mode

- 6. Timer mode

- 7. Counter and Timer mode

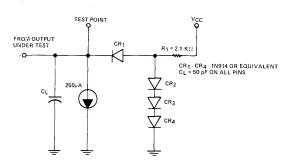

## **OUTPUT LOAD CIRCUIT**

## Figure 2

VII

# VII

## **ORDERING INFORMATION**

| PART NO.   | DESIGNATOR | PACKAGE TYPE | MAX CLOCK FREQUENCY | TEMPERATURE<br>RANGE |

|------------|------------|--------------|---------------------|----------------------|

| MK3882N    | Z80-CTC    | Plastic      | 2.5 MHz             |                      |

| MK3882P    | Z80-CTC    | Ceramic      | 2.5 MHz             |                      |

| MK3882N-4  | Z80A-CTC   | Plastic      | 4.0 MHz             | 0° to 70°C           |

| MK3882P-4  | Z80A-CTC   | Ceramic      | 4.0 MHz             |                      |

| MK3882P-10 | Z80-CTC    | Ceramic      | 4.0 MHz             | -40° to +85°C        |