#### **GENERAL DESCRIPTION**

HM2006 is a single chip CMOS voice recognition LSI circuit with the on-chip analog front end, voice analysis, recognition process and system control functions. A 9 isolated-word voice recognition system can be composed of external microphone, keyboard, 16K SRAM and some other components. Combined with the microprocessor, an intellengent recognition system can be built.

#### **FEATURES**

- · Single chip voice recognition CMOS LSI.

- Speaker-dependent isolates-word recognition system.

- · External 16K SRAM can be connected directly.

- Maximum 9 words can be recognized for one chip.

- Maximum 1.92 sec of word can be recognized.

- · Multiple-chip configuration is possible.

- · A microphone can be connected directly.

- Two control mode is supported: Manual mode and CPU mode.

- Response time: less than 300 ms.

- 5V single power supply.

- 48-pin PDIP, 52 pin PLCC, 48 pad bare chip.

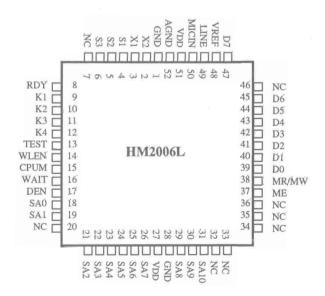

#### PIN CONFIGURATIONS

| HM2006P |                                                                                                                                     |                                                 |                                                                                            |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| GND     | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24 | 48 47 46 41 41 41 41 41 41 41 41 41 41 41 41 41 | AGND VDD MICIN LINE VREF D7 D6 D5 D4 D3 D2 D1 D0 MR/MW ME NC NC NC NC SA10 SA9 SA8 GND VDD |  |  |  |  |

## PIN DESCRIPTIONS

| Symbo           | l Pin No | ),   | I/O | Function                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|----------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | PDIP     | PLCC |     |                                                                                                                                                                                                                                                                                                                                                                               |

|                 | 48L      | 52L  |     |                                                                                                                                                                                                                                                                                                                                                                               |

| Vref            | 44       | 48   | Ι   | The voltage reference input of internal ADC. Supply the reference voltage of the internal A/D converter.                                                                                                                                                                                                                                                                      |

| LINE            | 45       | 49   | O   | For testing only.                                                                                                                                                                                                                                                                                                                                                             |

| MICIN           | 46       | 50   | I   | Microphone connect pin. A microphone should be connected via a coupling capacitor and resistor.                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub> | 47       | 51   |     | Positive power supply.                                                                                                                                                                                                                                                                                                                                                        |

| AGND            | 48       | 52   |     | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                |

| GND             | 1        | 1    |     | Negative power supply.                                                                                                                                                                                                                                                                                                                                                        |

| X2,X1           | 2,3      | 2,3  | I   | Crystal connect pin. A 3.58 MHz crystal is connected to these pin.                                                                                                                                                                                                                                                                                                            |

| S1,S2           | 4,5      | 4,5  | I/O | Keypad scaning pin for manual mode and the read/write                                                                                                                                                                                                                                                                                                                         |

| \$3             | 6        | 6    |     | control Pins in the CPU mode.                                                                                                                                                                                                                                                                                                                                                 |

| RDY             | 7        | 8    | О   | Voice input ready indicator. Active low output. When HM2006 is ready for the voice input in training or recognition mode, a low signal is sent. If the chip is busy, a high signal is sent.                                                                                                                                                                                   |

| K1,K2<br>K3,K4  | 8-11     | 9-12 | I/O | The keypad input pin in the manual mode and the bidirectional data bus (K-bus)in the CPU mode.                                                                                                                                                                                                                                                                                |

|                 |          |      |     | In the manual mode, the four pins combined with S1 to S3 form the keypad scaning circuit. Maximum12 keys can be scanned. In the CPU mode, the data bus direction is determined by the S2 and S3.A high level signal that appears in the pin S2 will place the content of internal register onto to the data bus.(K-bus).                                                      |

|                 |          |      |     | The data may be come from the status register or the output buffer which is selected by the pin S1. If S1 is high, output buffer is selected, otherwise, the status register is selected. A high level signal that appears in the pin S3 will place the content of K-bus into the input register. Note that user can not place high level signal on S2 and S3 simultaneously. |

| TEST            | 12       | 13   | I   | "H":test mode. "L":Normal mode.                                                                                                                                                                                                                                                                                                                                               |

| WLEN            | 13       | 14   | Ι   | Word length select pin.  Selecting the voice length to be recognized. When set to high, 1.92 sec is selected. Internally pull low for 0.9 sec is selected. Note that when 1.92 sec is selected, only 4 words maximum can be recognized.                                                                                                                                       |

| CPUM            | 14       | 15   | Ι   | CPU mode select pin. Internally pull low for manual mode. When set to high, CPU mode is selected.                                                                                                                                                                                                                                                                             |

|                 |          |      |     | Then set to mgh, et o mode is selected.                                                                                                                                                                                                                                                                                                                                       |

| Symbol                                                         | Pin No                     |                            | I/O | Function                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------|----------------------------|----------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                | PDIP 1                     | PLCC<br>52L                |     |                                                                                                                                                                                                                                                                                                                                                               |

| WAIT                                                           |                            | 16                         | I   | Waiting control input. Active low input. When this pin is set to "L" and manual mode is selectes, HM2006 will enter the waiting state and do not accept voice input until this pin back to "H". For CPU mode, when HM2006 is ready to get voice input, if this pin is set to "L", HM2006 will skip the voice input process and enter the get-commane process. |

| DEN                                                            | 16                         | 17                         | 0   | Data enable signal.  When the recognition or training process is complete, the chip will place its response on the data bus D0 to D7 and which can be latched onto external devices by this pin.                                                                                                                                                              |

| SA0,SA1<br>SA2-SA7<br>SA8-SA10<br>V <sub>DD</sub><br>GND<br>NC | 27-29<br>25<br>26<br>30-33 | 21-26<br>29-31<br>27<br>28 | 0   | External memory address bus.  The bus is used as an external memory address when ME pin is active.  Positive power supply.  Negative power supply.                                                                                                                                                                                                            |

| ME                                                             | 34                         | 37                         | 0   | Memory enable pin. Active low output. This pin will send the memory enable signal to the external SRAM. This pin can be connected directly to the CE pin of 6116 SRAM.                                                                                                                                                                                        |

| MR/MW                                                          | 35                         | 38                         | 0   | Memory read/write select pin.  Read/write control signal of the external SRAM. This pin can be connected directly to the R/W pin of 6116 SRAM.                                                                                                                                                                                                                |

| D0-D6<br>D7                                                    | 36-42<br>43                | 39-45<br>47                | I/O | External memory data bus(D-bus).  The bus is used as an external memory I/O bus when ME pin is active and used as output response bus when DEN pin is active.                                                                                                                                                                                                 |

#### **FUNCTION DESCRIPTIONS**

There are two operation mode which are provided by HM2006.

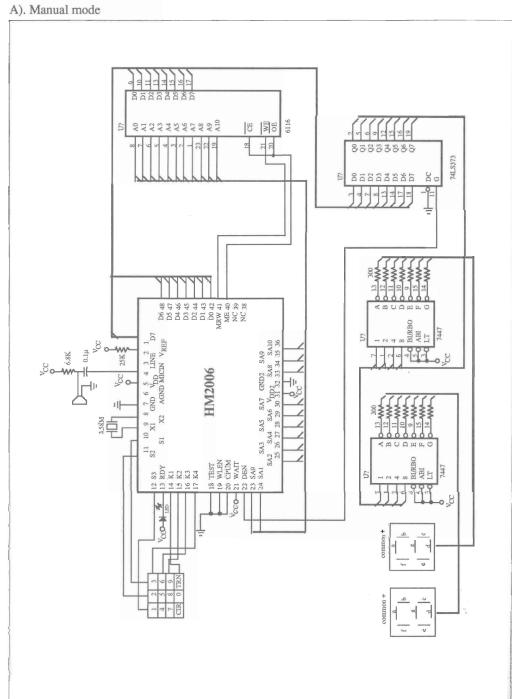

## A). Manual mode.

In this operation mode, a keypad, a SRAM and other components may be connected to HM2006 to build a simple recognition system (See application circuit). The type of SRAM can be used is a 2K-byte memory.

#### a). Power on.

When the power is on,HM2006 will start its initialization process. If WAIT pin is "L", HM2006 will do the memory check to see whether the external 2K byte SRAM is perfect or not.

If WAIT pin is "H", HM2006 will skip the memory check process.

After the initial process is done, HM2006 will then move into recogition mode.

### b). Recognition Mode.

## i). WAIT pin "H"

In this mode, the RDY is set to low and HM2006 is ready to accept the voice input to be recognized.

When the voice input is detected, the RDY will return to high and HM2006 begins its recognition process. It is recommended that user train the word pattern before the beginning of the recognition operation, otherwise the result will be unpredictable. After the recognition process is completely, the result will appear on the D-bus with the pin DEN active.

Table 1 shows the list of the output content.

The data on the data bus is a decimal code in binary format.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Description     |

|----|----|----|----|----|----|----|----|-----------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Power on        |

|    |    | A  |    |    |    | В  |    | Word AB         |

| 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | Voice too long  |

| 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | Voice too short |

| 0  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | Not Match       |

Table 1: Content of the D-bus output.

Note 1: A is the binary code and can be zero only, and B is the binary code in the range 1 to 9.

Note 2: If WLEN is high, the maximum word length is 1.92 sec.

## ii).WAIT pin "L"

In this mode, no voice input is accepted until WAIT pin back to "H" state.

# c). Training or clearing one pattern

Two operation are included during this time, 1) clearing trained pattern and 2) training new pattern.

To clear or train the voice pattern, one must select the word number to process first. The number of word is composed of two digits. The two digits are entered into HM2006 through keypad one digit a time. If more than two digits are entered, only the last two digits are valid. When number key is pressed, the number of key will be echoed to the D-bus.

When the word number is entered, press the function key to choose the operation function. If function key CLR is pressed, the corresponding word pattern will be cleared and then HM2006 will return its recognition mode. If the function key TRN is pressed, HM2006 will begin its training process. At the beginning of training process, if WAIT pin is "H", HM2006 will send a low level signal to RDY to indicate that HM2006 is ready to accept voice input. If WAIT pin is "L", no voice input will be detected until WAIT pin back to "H". After available voice input to HM2006, HM2006 will return to its recognition mode and send a low level signal to RDY to indicate that HM2006 is ready for voice input to do the recognition process.

For example.

- 0.8 TRN  $\rightarrow$  training the 8th pattern.

- 0.1 CLR  $\rightarrow$  clearing the first pattern.

- 1 3 0 9 TRN → training the 9th pattern.

#### d). Clear all pattern.

If the number key 99 is entered and the CLR is pressed, all the patterns in the memory will be cleared by HM2006.

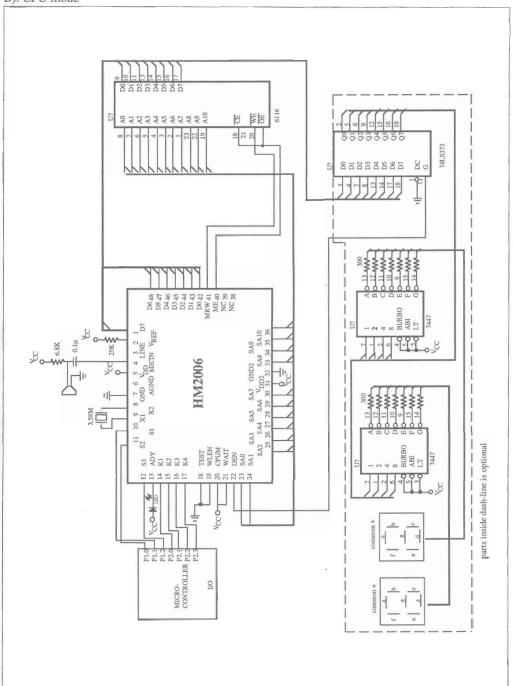

## B). CPU control mode.

The CPU mode provides several functions: RECOG, TRAIN, RESULT, UPLOAD, DOWNLOAD, RESET and which will be described later. In this mode, the K-bus is used as a bidirectional data bus between the external controller and HM2006 and S1 to S3 as the R/W control pins.

Table 2 is the summary of the CPU command. The command contains two parts, 1), the command code and 2), the number of the word to be processed if needed.

| command  | code | word #(L)   | word #(H) |

|----------|------|-------------|-----------|

| RECOG    | 0001 |             |           |

| TRAIN    | 0010 | B3 B2 B1 B0 | 0 0 B5 B4 |

| RESULT   | 0100 |             |           |

| UPLOAD   | 0101 | B3 B2 B1 B0 | 0 0 B5 B4 |

| DOWNLOAD | 0110 | B3 B2 B1 B0 | 0 0 B5 B4 |

| RESET    | 0111 |             |           |

Table 2. Command for CPU mode.

There are three registers in HM2006, one input buffer register, one status register and one output buffer register. The first is a write-only register and the last two are read-only registers. If S1 pin is high, the data read from the K-bus will come from the output buffer register. If S1 pin is low, the data read from the K-bus will come from the status register. S2 and S3 are R/W control signals. If S2 is high, it's in a read cycle and the external controller can read data form the K-bus. If S3 is high, it's in a write cycle and external controller can write data into the input buffer. Note that S2 and S3 can not be high simultaneously and the state of S1 will be ignored during a write cycle.

The status register as shown, reflect the current status of HM2006 for the CPU control mode.

27

92

C1

CU

| 93  | 02  | 91  | 30  |                                                        |

|-----|-----|-----|-----|--------------------------------------------------------|

| X   | X   | ST1 | ST0 |                                                        |

|     |     |     |     |                                                        |

| ST1 | ST0 |     |     | Operating state:                                       |

| 0   | 1   |     |     | Ready to get voice input.                              |

| 1   | 0   |     |     | Ready to get command.                                  |

| 1   | 1   |     |     | 1. The first nibble of the output data is available on |

|     |     |     |     | the output buffer during a read cycle.                 |

|     |     |     |     | 2. HM2006 is ready to get first nibble of the input    |

|     |     |     |     | data during a write cycle.                             |

| 0   | 0   |     |     | 1. The second nibble of the output data is available   |

|     |     |     |     | on the output buffer during a read cycle.              |

|     |     |     |     | 2. HM2006 is ready to get second nibble of the input   |

data during a write cycle.

#### a). Power on

When power is on, the chip will perform its initialization process, the same as manual mode and then make the status register to be (10) to wait the external command.

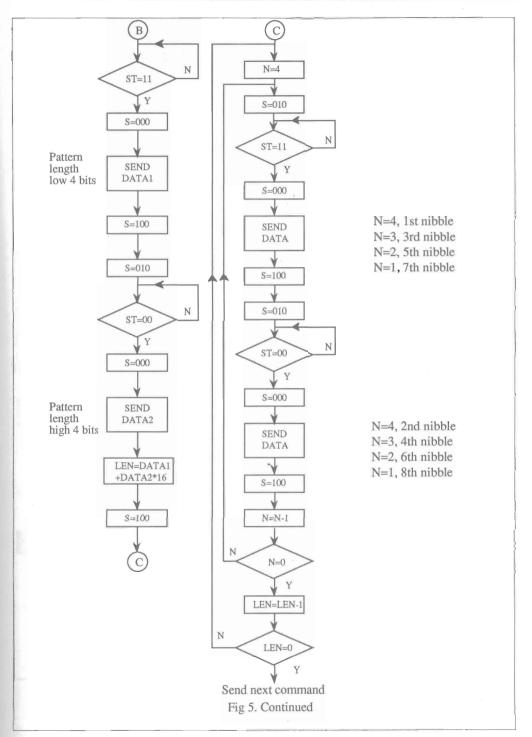

## b). Recognition.

When HM2006 receives the command RECOG, the chip will begin its recognition process. The external device can be polling the status flag to monitor the operation state of HM2006. When the operation state is changed to (01), and WAIT pin is "L", HM2006 will back to the operation state (10) and then ready for receive another command. When the operation state is change to (01) and WAIT pin is "H", it is ready to get voice input and then do the recognition process. When the operation state is changed back to (10) again, then the recognition process is completed and HM2006 is ready to get another command. The programming flow chart is shown in Fig. 1.

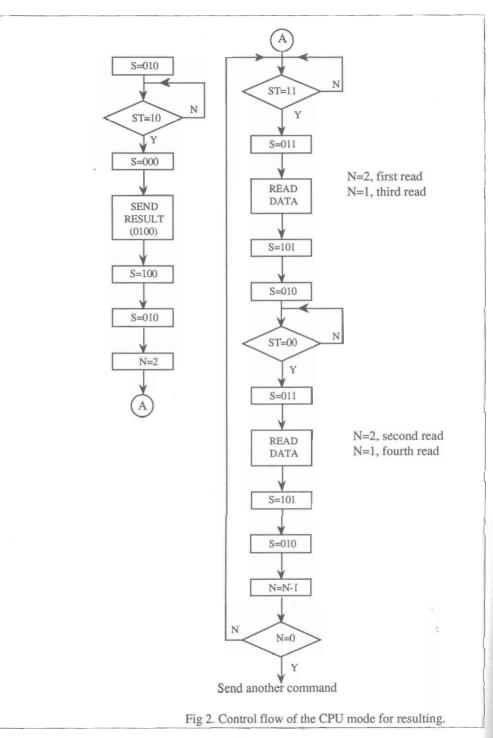

# c). Resulting

After recognition, the recognition result is ready in the buffer. The external device can send the RESULT command to obtain the recognition result. When the data in the buffer has been read, the operation state will be turned back (10) and waiting for another command.

When the RESULT command is sent, four continuous read actions must be done by the external device to get the result sent by HM2006. The result contains two parts, each parts needs two read actions. The first part is the word number (B5-B0) and the second part is the matching score (V7-V0).

Table 3 shows the output format of the result and the programming control flow chart is shown in Fig 2.

| 1st read    | 2nd read  | 3rd read    | 4th read    | Result            |

|-------------|-----------|-------------|-------------|-------------------|

| B3 B2 B1 B0 | 0 0 B5 B4 | V3 V2 V1 V0 | V7 V6 V5 V4 | Word # and Score. |

Table 3.

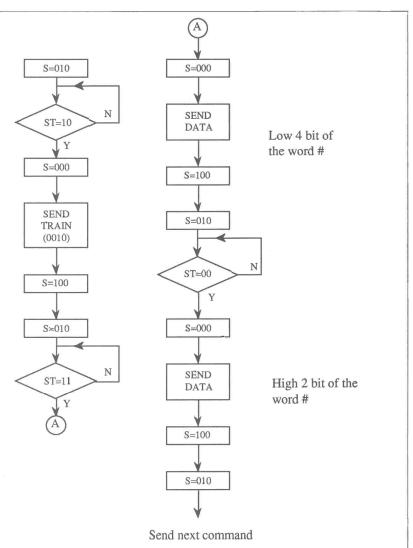

#### d). Training Pattern

When HM2006 receives the command code TRAIN, the chip needs two more words to specify the number of pattern to be trained. The first word is the low 4 bit of the word number and the second word is the high 2 bits of the word number.

If the number of the pattern is valid and WAIT pin is "H", HM2006 will begin its training process for the corresponding word. If WAIT is "L", HM2006 will skip the training process. After the training process, the operation state will change back to (10) and wait for next command. Fig 3 shows the control flow of the training process.

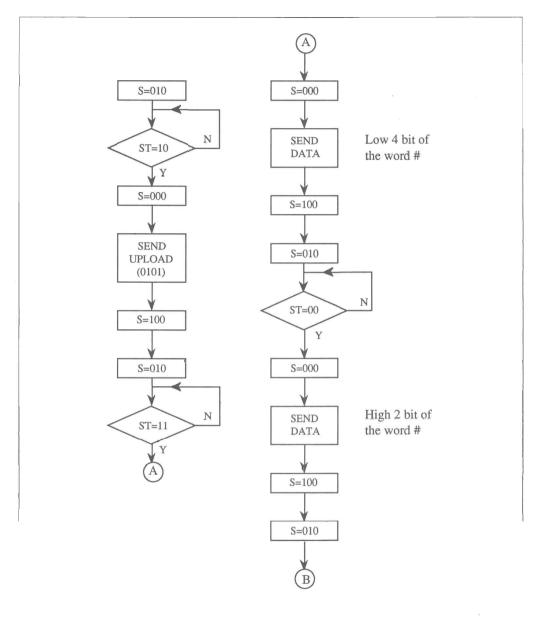

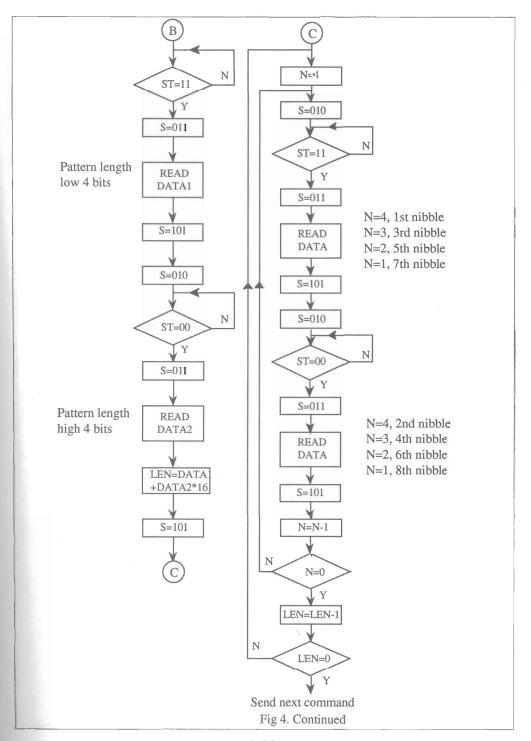

## e). Upload pattern

When HM2006 receives the command code UPLOAD, the chip needs two more words to specify the number of pattern to be uploaded. The first word is the low 4 bits of the word number and the second word is the high 2 bits of the word number.

In the uploading process,HM2006 will send the pattern length first in two words(low 4 bits first, then high 4 bits), and then the data of the pattern frame by frame and each frame is consisted of eight words (4 bits). Fig 4 shows the control flow chart of the uploading process. Note that when the external device get the data which is sent by HM2006, it's user's responsibility to designate a memory space to save them, otherwise, the data will be lost and no use of this command.

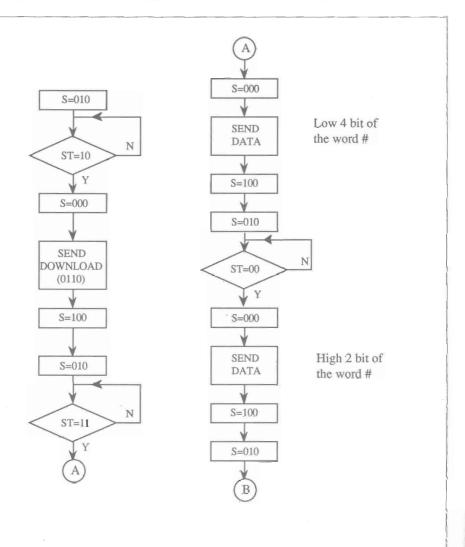

# f). Download pattern

The download pattern process is same as the upload pattern process except that the direction of the data flow is reversed. After receiving the DOWNLOAD command and the word number, HM2006 begin to read data from external device. The first two words of the data will be treated as the pattern length and the following data will be stored as pattern frame by frame. Fig 5 shows the control flow of the downloading process.

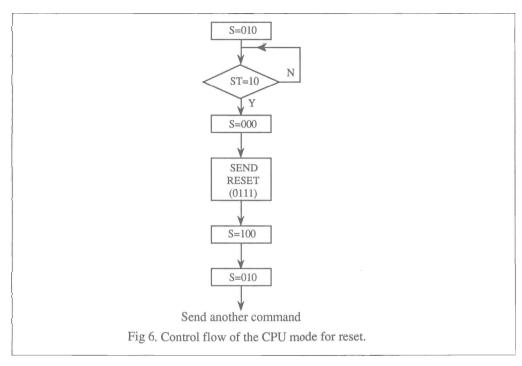

# g). Reset

When Reset command is received by HM2006, the chip will clear all the patterns in the memory. Fig 6 shows the control flow of reset process.

Fig 1. Control flow of the CPU mode for recognition.

Fig 3. Control flow of the CPU mode for training.

Fig 4. Control flow of the CPU mode for uploading.

Fig 5. Control flow of the CPU mode for downloading.

#### ABSOLUTE MAXIMUM RATINGS

| Sym.     | Lim<br>Min.            | itation<br>Max.                  | Unit                                                       |

|----------|------------------------|----------------------------------|------------------------------------------------------------|

| $V_{DD}$ | -0.3                   | +6.0                             | V                                                          |

| Vin      | -0.3                   | $V_{DD} + 0.3$                   | V                                                          |

| Top      | -20                    | +70                              | °C                                                         |

| Tstg     | -55                    | +125                             | °C                                                         |

|          | V <sub>DD</sub><br>Vin | V <sub>DD</sub> -0.3<br>Vin -0.3 | V <sub>DD</sub> -0.3 +6.0<br>Vin -0.3 V <sub>DD</sub> +0.3 |

# DC ELECTRICAL CHARACTERISTICS $(T_A=25^{\circ}C, V_{ss}=0V)$

| Items                     | Sym.            | Min. | Тур. | Max. | Unit | Conditions                   |

|---------------------------|-----------------|------|------|------|------|------------------------------|

| Supply Voltage            | $V_{DD}$        | 4.0  | 5.0  | 5.5  | V    |                              |

| Operating Current         | $I_{DDO}$       | -    | 6    | 15   | mA   | V <sub>DD</sub> =5V, no load |

| Output Drive Current      | $I_{OH}$        | 0.5  | 1.5  | -    | mA   | Vo=4.6V                      |

| Output Sink Current       | I <sub>OL</sub> | 0.5  | 1.5  | -    | mA   | Vo=0.4V                      |

| Output Current of RDY     | $I_{RDY}$       | 5.0  | 8.0  | -    | mA   | $V_{RDY} = 3.35V$            |

| Input Leakage Current     | $I_{LKG}$       | -    | 0.1  | 1.0  | μΑ   | Vi=4.6V                      |

| Input Current (Pull Down) | I               | 50   | 200  | 300  | μΑ   | Vi=4.6V                      |

|                           |                 |      |      |      |      |                              |

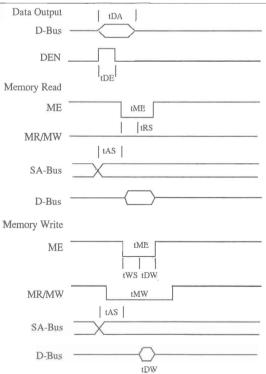

# AC ELECTRICAL CHARACTERISTICS

| Items                    | Sym. | Min. | Тур. | Unit |

|--------------------------|------|------|------|------|

| Data Output              |      |      |      |      |

| Output Data Enable Width | tDE  | 240  | 280  | ns   |

| Output Data Holding Time | tDA  | 440  | 480  | ns   |

| Memory Read              |      |      |      |      |

| Memory Enable Width      | tME  | 520  | 560  | ns   |

| Address Setup Time       |      |      |      |      |

| to Memory Enable         | tAS  | 240  | 280  | ns   |

| Memory Enable to Data    |      |      |      |      |

| Reading Starting         | tRS  | 240  | 280  | ns   |

| Memory Write             |      |      |      |      |

| Memory Enable Width      | tME  | 520  | 560  | ns   |

| Memory Write Signal      |      |      |      |      |

| Width                    | tMW  | 1080 | 1120 | ns   |

| Address Setup Time       |      |      |      |      |

| to Memory Enable         | tAS  | 240  | 280  | ns   |

| Memory Enable to Data    |      |      |      |      |

| Writing Starting         | tWS  | 240  | 280  | ns   |

| Data Write Period        | tDW  | 240  | 280  | ns   |

|                          |      |      |      |      |

#### APPLICATION CIRCUIT

B). CPU mode

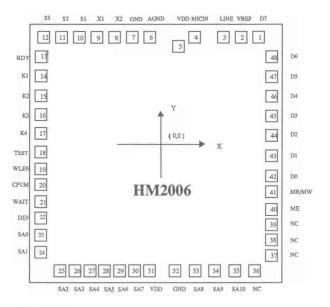

#### **PAD DIAGRAM**

Chip Size : 3970  $\mu m \times 3890 \mu m$

| Pad No. | Name             | X       | Y       |

|---------|------------------|---------|---------|

| 1       | D7               | 1722.6  | 1719.6  |

| 2       | V <sub>REF</sub> | 1503.8  | 1720.0  |

| 3       | LINE             | 1220.6  | 1720.0  |

| 4 5     | MICIN            | 838.2   | 1720.0  |

| 5       | V <sub>DD</sub>  | 618.3   | 1666.1  |

| 6       | AGND             | -7.1    | 1647.1  |

| 7       | GND              | -296.2  | 1645.2  |

| 8       | X2               | -597.7  | 1720.1  |

| 9       | X1               | -922.9  | 1720.0  |

| 10      | S1               | -1204.1 | 1720.0  |

| 11      | S2               | -1485.3 | 1720.0  |

| 12      | S3               | -1766.5 | 1720.0  |

| 13      | RDY              | -1799.6 | 1468.0  |

| 14      | K1               | -1799.6 | 1198.4  |

| 15      | K2               | -1799.6 | 937.8   |

| 16      | K3               | -1799.6 | 668.8   |

| 17      | K4               | -1799.6 | 408.2   |

| 18      | TEST             | -1800.0 | 184.8   |

| 19      | WLEN             | -1800.0 | -94.9   |

| 20      | CPUM             | -1800.0 | -408.2  |

| 21      | WAIT             | -1800.0 | -721.2  |

| 22      | DEN              | -1799.6 | -1046.4 |

| Pad No. | Name           | X       | V       |

|---------|----------------|---------|---------|

|         |                |         |         |

| 23      | SA0            | -1799.6 | -1316.0 |

| 24      | SA1            | -1799.6 | -1576.6 |

| 25      | SA2            | -1459.7 | -1759.6 |

| 26      | SA3            | -1186.1 | -1759.6 |

| 27      | SA4            | -922.1  | -1759.6 |

| 28      | SA5            | -648.5  | -1759.6 |

| 29      | SA6            | -384.5  | -1759.6 |

| 30      | SA7            | -110.9  | -1759.6 |

| 31      | $V_{_{ m DD}}$ | 180.1   | -1760.1 |

| 32      | GND            | 409.4   | -1760.0 |

| 33      | SA8            | 723.9   | -1759.6 |

| 34      | SA9            | 987.9   | -1759.6 |

| 35      | SA10           | 1261.5  | -1759.6 |

| 36      | NC             | 1525.5  | -1759.6 |

| 37      | NC             | 1799.6  | -1592.3 |

| 38      | NC             | 1800.0  | -1267.1 |

| 39      | NC             | 1800.0  | -983.9  |

| 40      | ME             | 1799.6  | -761.9  |

| 41      | MR/MW          | 1799.6  | -488.3  |

| 42      | D0             | 1799.6  | -224.3  |

| 43      | D1             | 1799.6  | 49.3    |

| 44      | D2             | 1799.6  | 313.3   |

| 45      | D3             | 1799.6  | 586.9   |

| 46      | D4             | 1799.6  | 850.9   |

| 47      | D5             | 1799.6  | 1124.5  |

| 48      | D6             | 1799.6  | 1388.5  |

Unit :  $\mu m$  Note : The substrate must be connected to  $\boldsymbol{V}_{\text{SS}}$  in PCB layout artwork.